Question: code 1 :library ieee; use ieee.std _ logic _ 1 1 6 4 . all; entity D _ ff is port ( clk : in

code :library ieee;

use ieee.stdlogicall;

entity Dff is

port

clk : in bit;

d : in bit;

reset : in bit;

qout : out bit

;

end Dff;

architecture Behavioral of Dff is

signal qint : bit :;

begin

process clk reset

begin

if reset then

qint ;

elsif clk'event and clk then

qint d;

end if;

end process;

Copy

qout qint;

end Behavioral; code :library ieee;

use ieee.stdlogicall;

entity mux is

Port

a : in bitvector downto ;

b : in bit;

c : out bit

;

end mux;

architecture Behavioral of mux is

begin

c a when b else a;

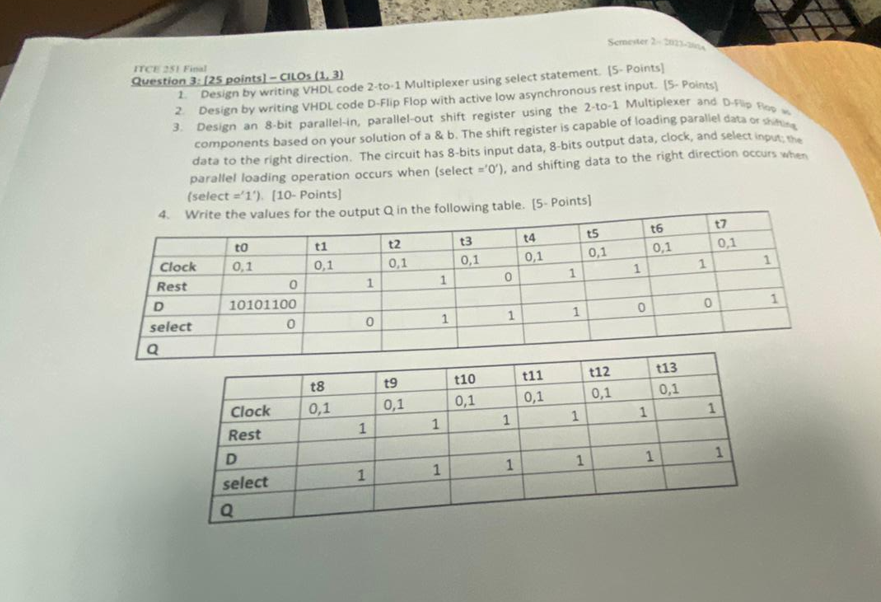

end Behavioral; use these two codes as a component to design a top level code fot bit parallel in and parallel out shift register the shift register is capable of loading parallel data or shifting data to the right direction the cicuit has bits input data and bit output data clock and select input the parallel loading operation occures when select and shifting data to the right direction occurs when select

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock