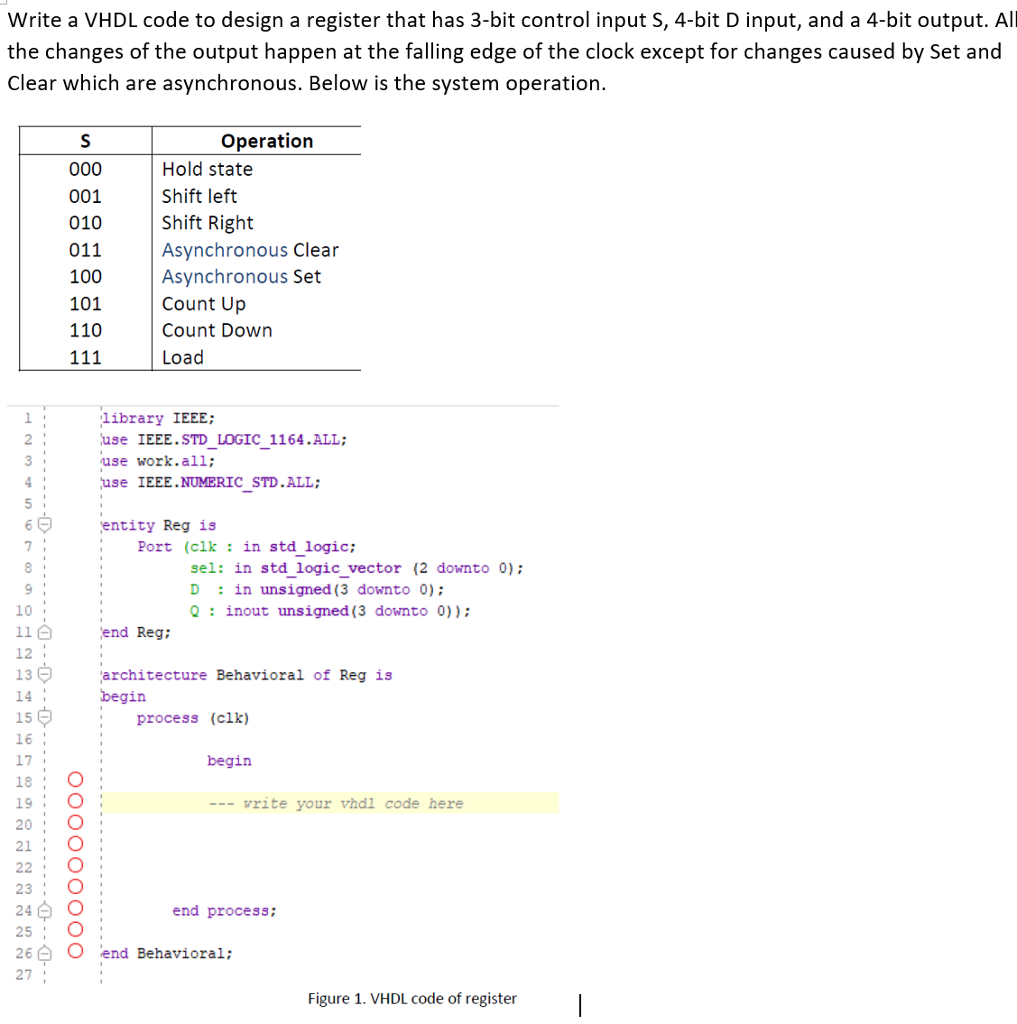

Question: Write a VHDL code to design a register that has 3-bit control input S, 4-bit D input, and a 4-bit output. All the changes of

Write a VHDL code to design a register that has 3-bit control input S, 4-bit D input, and a 4-bit output. All the changes of the output happen at the falling edge of the clock except for changes caused by Set and Clear which are asynchronous. Below is the system operation. Operatiorn 001 010 011 100 101 110 Hold state Shift left Shift Right Asynchronous Clear Asynchronous Set Count Up Count Down Load library IEEE; use IEEE.STD LOGIC 1164.ALL use work.all; use IEEE.NUMERIC STD.ALL 2 entity Reg is Port (clk:in stdlogic; sel: in std_logic vector (2 downto 0) Din unsigned (3 downto 0) Qinout unsigned (3 downto 0)); 9 11d Reg: 12 13 14 15 16 17 18O 19O 20O 21 O 22 O 23 O 24 0 : architecture Behavioral of Reg is begin process (clk) begin vrite your vhdl code here end process: 25 26 O end Behavioral; 27 Figure 1. VHDL code of register Write a VHDL code to design a register that has 3-bit control input S, 4-bit D input, and a 4-bit output. All the changes of the output happen at the falling edge of the clock except for changes caused by Set and Clear which are asynchronous. Below is the system operation. Operatiorn 001 010 011 100 101 110 Hold state Shift left Shift Right Asynchronous Clear Asynchronous Set Count Up Count Down Load library IEEE; use IEEE.STD LOGIC 1164.ALL use work.all; use IEEE.NUMERIC STD.ALL 2 entity Reg is Port (clk:in stdlogic; sel: in std_logic vector (2 downto 0) Din unsigned (3 downto 0) Qinout unsigned (3 downto 0)); 9 11d Reg: 12 13 14 15 16 17 18O 19O 20O 21 O 22 O 23 O 24 0 : architecture Behavioral of Reg is begin process (clk) begin vrite your vhdl code here end process: 25 26 O end Behavioral; 27 Figure 1. VHDL code of register

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts