Question: Complete the behavioral VHDL code of an Arithmetic Logic Unit that has 4 inputs A, B, f and EN. A and B are 16 bits

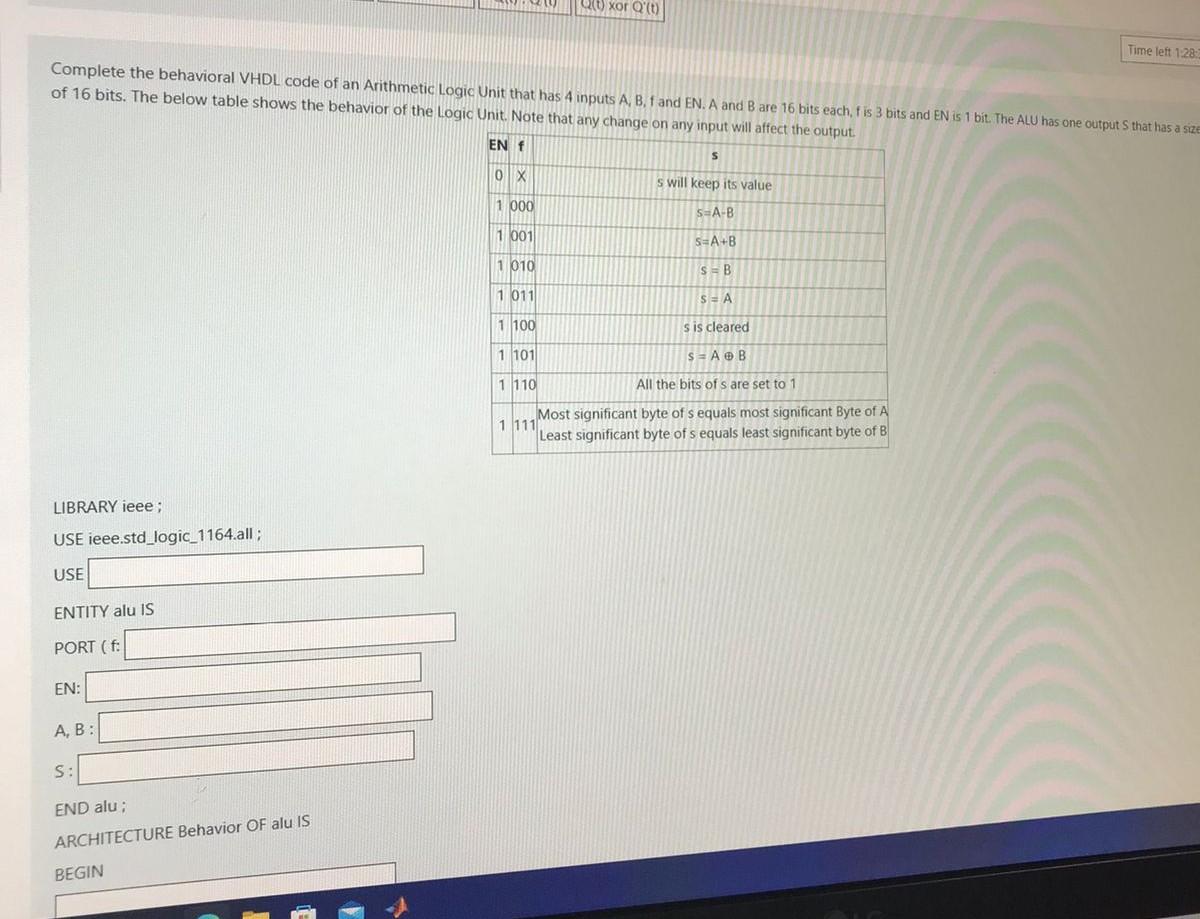

Complete the behavioral VHDL code of an Arithmetic Logic Unit that has 4 inputs A, B, f and EN. A and B are 16 bits each, f is 3 bits and EN is 1 bit. The ALU has one output S that has a sit of 16 bits. The below table shows the behavior of the Logic Unit. Note that any change on any input will affect tha nitnut LIBRARY ieee; USE ieee.std_logic_1164.all : USE ENTITY alu IS PORT (f: EN A,B : S: END alu: ARCHITECTURE Behavior OF alu IS BEGIN

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts