Question: Computer Architecture CENG 3531 Fall 2015 ENG 3351 Computer Architecture Fall 2015 8. (20 pts) Considering the classic 5-stage MIPS pipeline, show the pipeline diagram

Computer Architecture

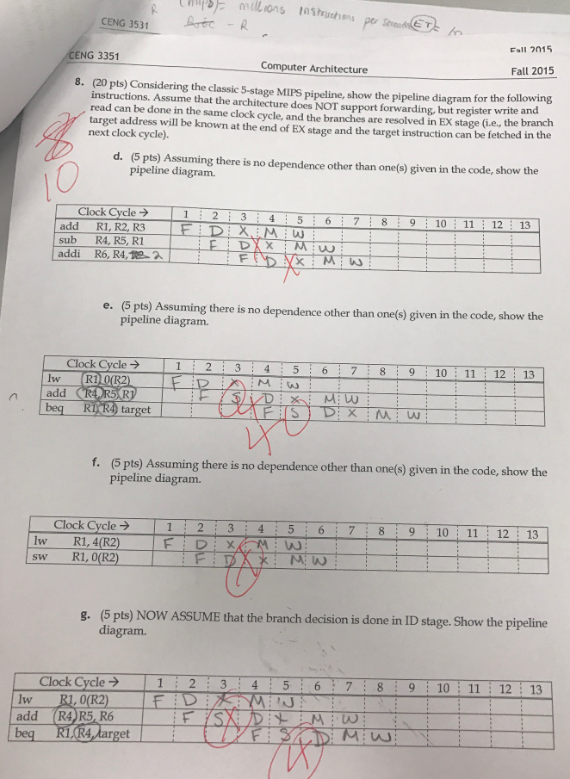

CENG 3531 Fall 2015 ENG 3351 Computer Architecture Fall 2015 8. (20 pts) Considering the classic 5-stage MIPS pipeline, show the pipeline diagram for the following instructions. Assume that the architecture does NOT support forwarding, but register write and read can be done in the same clock cycle, and the branches are resolved in EX stage (i.e, the branch target address will be known at the end of EX stage and the target instruction can be fetched in the next clock cycle). d. (5 pts) Assuming there is no dependence other than one(o) given in the code, show the 0 pipeline diagram. Clock Cycle add sub R1, R2, R3-FD- R4, R5, R1 6 pts) Assuming there is no dependence other than one(s) given in the code, show the pipeline diagram. n add . (5 pts) Assuming there is no dependence other than oneo) given in the code, show the pipeline diagram. 12345678 9:1011 12 13 SW R1, 0(R2) A) (5 pts) NOW ASSUME that the branch decision is done in ID stage. Show the pipeline diagram. g. lw add R4 R5, R R2 DM:W

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts