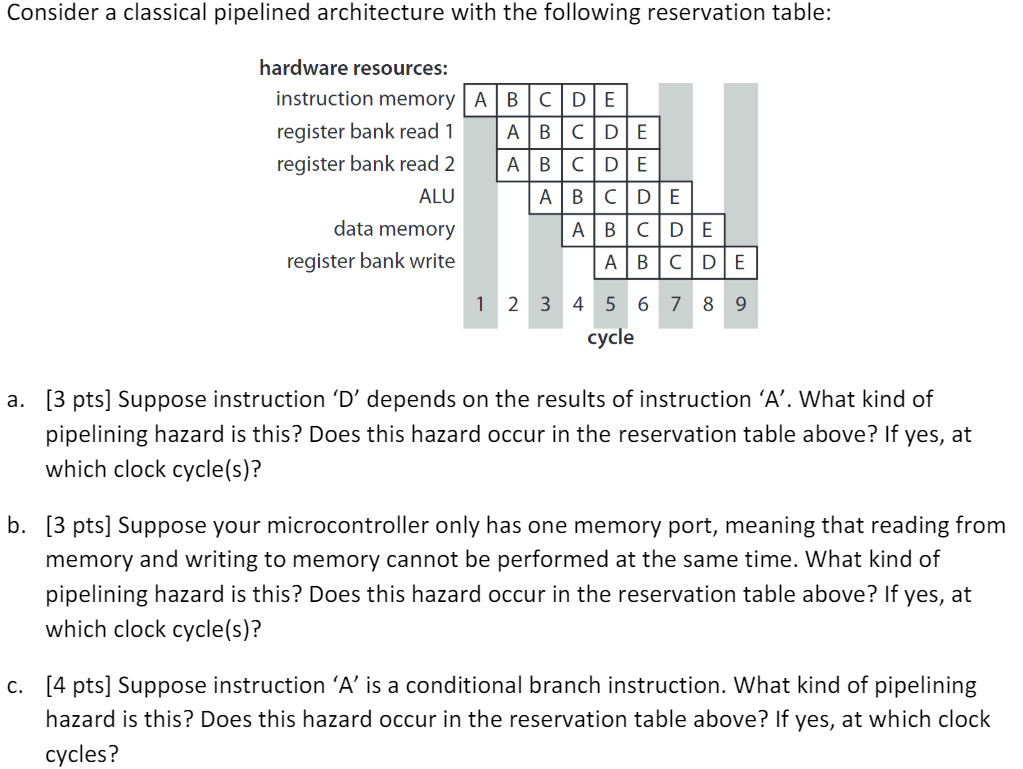

Question: Consider a classical pipelined architecture with the following reservation table: hardware resources: instruction memory register bank read 1 register bank read 2 ALU data memory

Consider a classical pipelined architecture with the following reservation table:

hardware resources:

instruction memory

register bank read

register bank read

ALU

data memory

register bank write

a Suppose instruction depends on the results of instruction What kind of

pipelining hazard is this? Does this hazard occur in the reservation table above? If yes, at

which clock cycles

b Suppose your microcontroller only has one memory port, meaning that reading from

memory and writing to memory cannot be performed at the same time. What kind of

pipelining hazard is this? Does this hazard occur in the reservation table above? If yes, at

which clock cycles

c Suppose instruction A is a conditional branch instruction. What kind of pipelining

hazard is this? Does this hazard occur in the reservation table above? If yes, at which clock

cycles?

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock