Question: Consider a pipeline with forwarding, hazard detection, and 2 cycles delay for branch taken. The pipeline is the typical 5-stage IF. ID, EX, MEM. WB

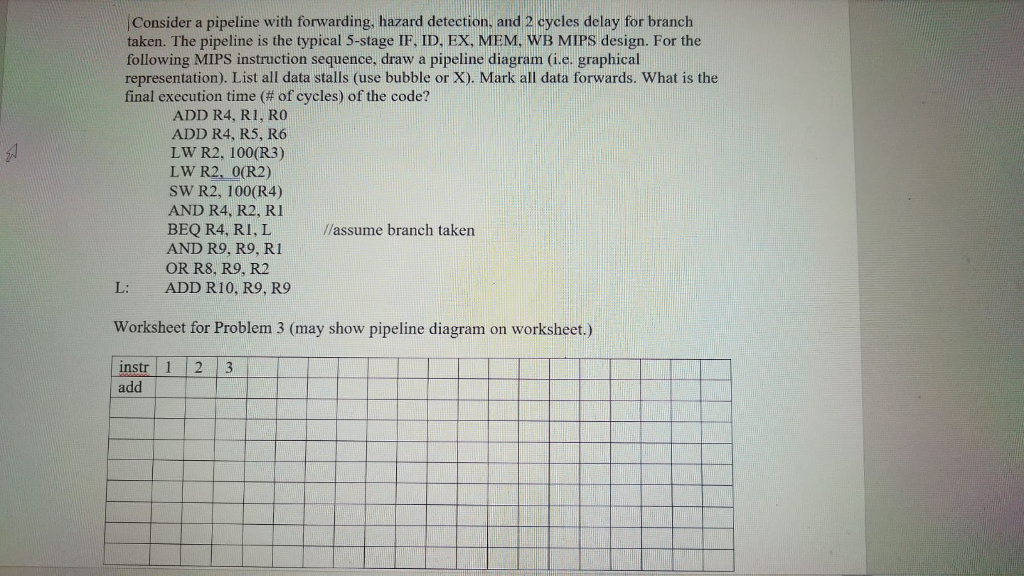

Consider a pipeline with forwarding, hazard detection, and 2 cycles delay for branch taken. The pipeline is the typical 5-stage IF. ID, EX, MEM. WB MIPS design. For the following MIPS instruction sequence, draw a pipeline diagram (i.e. graphical representation). List all data stalls (use bubble or X). Mark all data forwards. What is the final execution time (# of cycles) of the code? ADD R4, R1, RO ADD R4, R5, R6 LW R2, 100(R3) LW R2, 0(R2) SW R2, 100(R4) AND R4, R2, RI BEQ R4, RI. L AND R9, R9, R1 OR R8, R9, R2 /lassume branch taken L: ADD R10, R9, R9 Worksheet for Problem 3 (may show pipeline diagram on worksheet.) instr 12 3 add

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock