Question: Consider a two-level cache. In 1000 memory references, there are 50 misses in the first level and 10 misses in the second level. Assume the

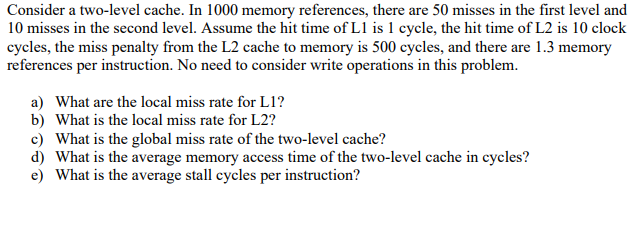

Consider a two-level cache. In 1000 memory references, there are 50 misses in the first level and 10 misses in the second level. Assume the hit time of LI is l cycle, the hit time of L2 is 10 clock cycles, the miss penalty from the L2 cache to memory is 500 cycles, and there are 1.3 memory references per instruction. No need to consider write operations in this problem. a) What are the local miss rate for L1? b) What is the local miss rate for L2? c) What is the global miss rate of the d) What is the average memory access time of the two-level cache in cycles? e) What is the average stall cycles per instruction? two-level cache

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts