Question: Consider the 4-bit shift register with parallel outputs and synchronous reset (reset brings the register to 0000 state on the rising edge of clock)

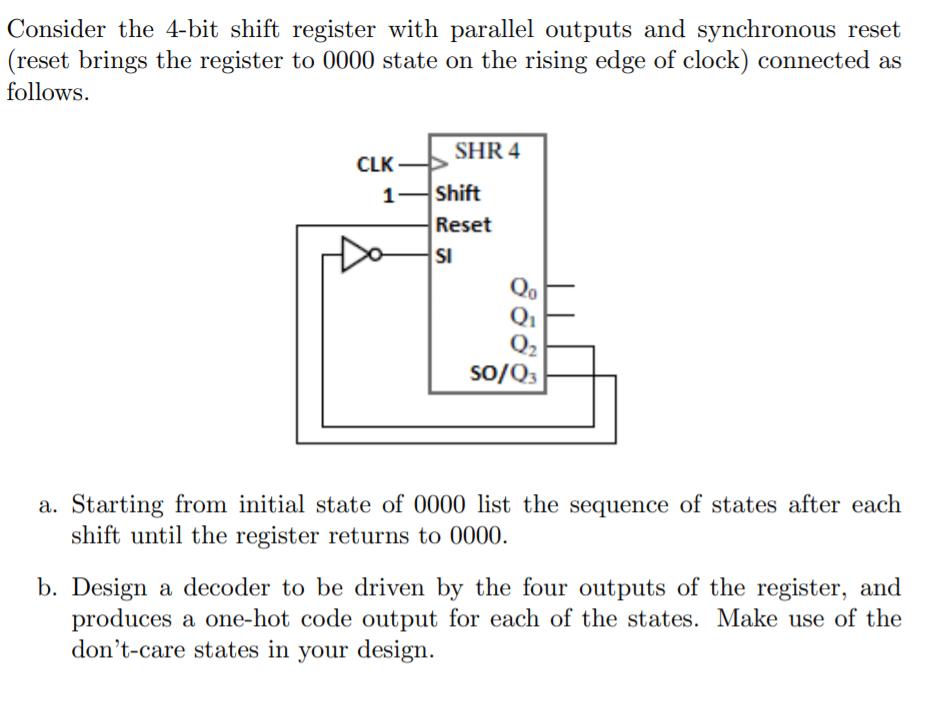

Consider the 4-bit shift register with parallel outputs and synchronous reset (reset brings the register to 0000 state on the rising edge of clock) connected as follows. SHR 4 CLK 1- Shift Reset SI Qo Q1 Q2 so/Q3 a. Starting from initial state of 0000 list the sequence of states after each shift until the register returns to 0000. b. Design a decoder to be driven by the four outputs of the register, and produces a one-hot code output for each of the states. Make use of the don't-care states in your design.

Step by Step Solution

3.33 Rating (147 Votes )

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts