Question: Consider the final MIPS single cycle implementation below. Assume that each of the logic block used in the processor's datapath has the following latencies. Register

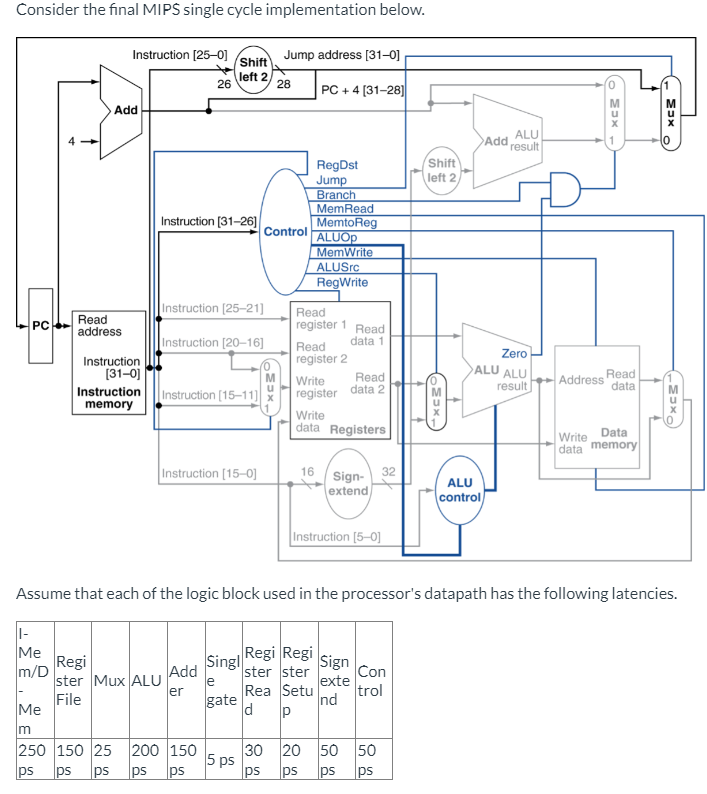

Consider the final MIPS single cycle implementation below.

Assume that each of the logic block used in the processor's datapath has the following latencies.

"Register read" is the time needed after the rising clock edge for the new register value to appear on the output. This value applies to the PC only. "Register setup" is the amount of time a register's data input must be stable before the rising edge of the clock. This value applies to both the PC and Register File.

Assuming these values, answer the following questions. Write your explanations for obtaining each answer. For each question, indicate the critical path.

aWhat is the latency of an Rtype instruction ie how long must the clock period be to ensure that this instruction works correctly

bWhat is the latency of lw

c What is the latency of sw

dWhat is the latency of beq?

eWhat is the latency of an arithmetic, logical or shift Itype nonload instruction?

fWhat is the minimum clock period for this CPU?

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock