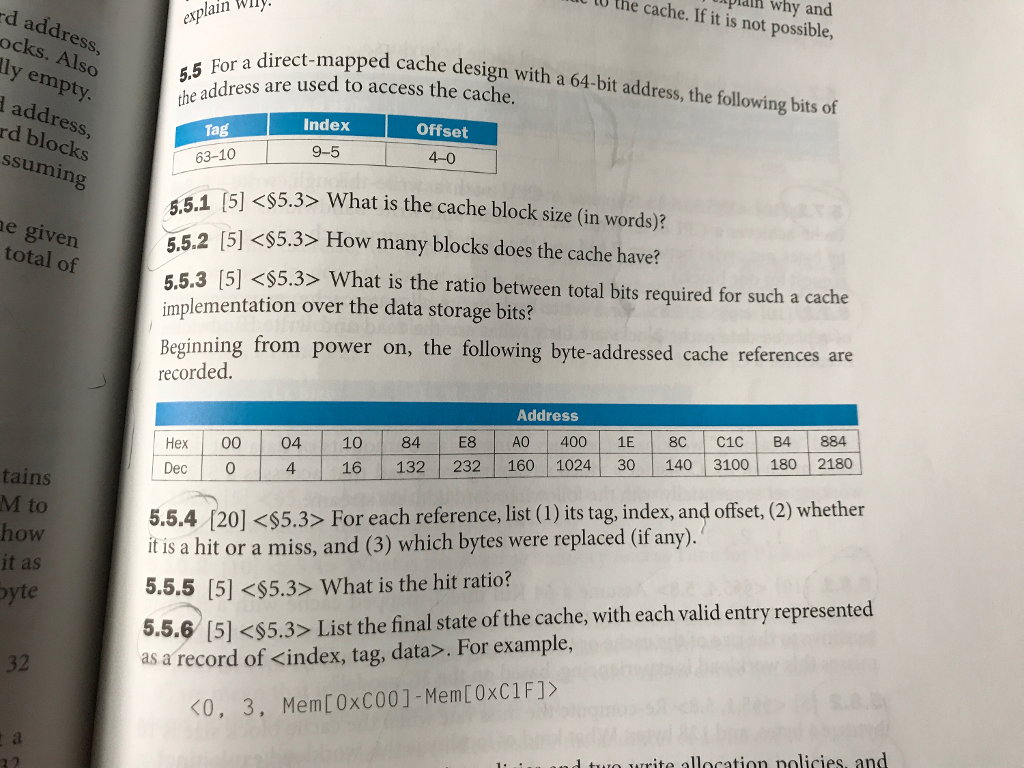

Question: for a direct mapped cache design with a 64-bit address the following bits of the address are used to access the cahe. Need help with

for a direct mapped cache design with a 64-bit address the following bits of the address are used to access the cahe. Need help with 5.5.4 and 5.5.6

l why and tu the cache. If it is not possible, explain WI d address ocks. Also ly empty address rd blocks direct-mapped cache design with a 64-bit address, the following bits of or a ddress are used to access the cache. Index Offset Tag 9-5 4-0 63-10 ssumin 5,5.1 5 What is the cache block size (in words)? 5.5.2 (51 How many blocks does the cache have? 55.3 [5]

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts