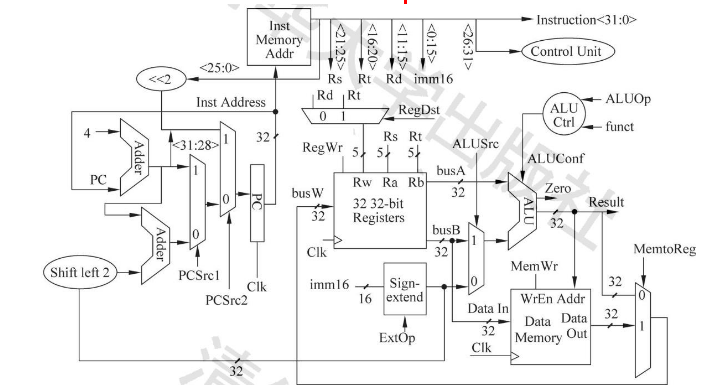

Question: For the single - cycle datapath in Figure 1 , all flip - flops are written on the clock rising edge, and the delay of

For the singlecycle datapath in Figure all flipflops are written on the clock rising edge, and the delay of each unit is listed as follow : memory:psALU and adder:psRegister file: read psRegister file: setup psMUX:PSControl unit & ALU control unit:psCalculate the execution time of the add, beq, and lw instructions, respectively ignore the delay of the

decoder and generating the control signals also, which units can tolerate more latency ie these units are not on the critical path What is the maximum frequency that the processor can run at

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock