Question: I got the unsigned portion but not the signed comparator. We are using verilog PART 5 - Design an unsigned 3-bit comparator such that A

I got the unsigned portion but not the signed comparator. We are using verilog

I got the unsigned portion but not the signed comparator. We are using verilog

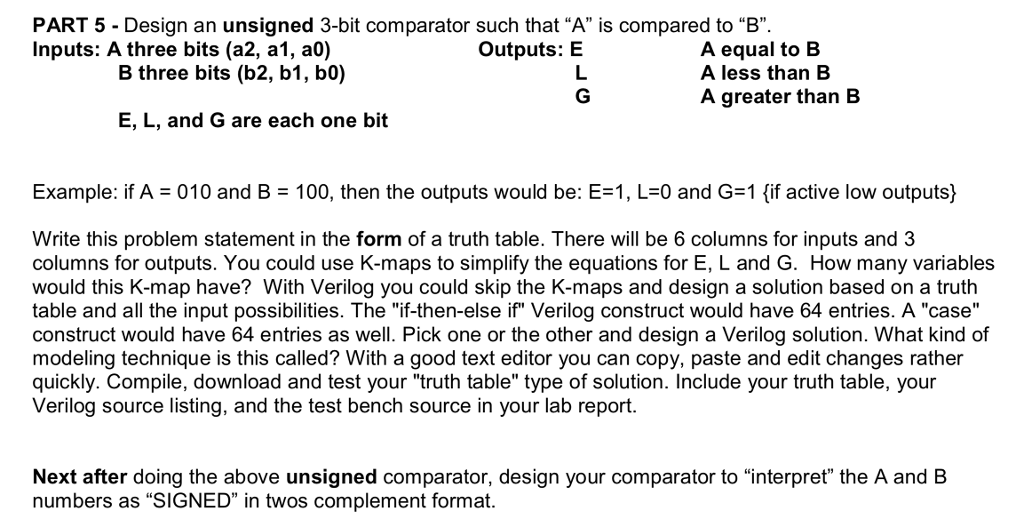

PART 5 - Design an unsigned 3-bit comparator such that "A" is compared to "B Inputs: A three bits (a2, a1, a0) Outputs: E A equal to B A less than B A greater than B B three bits (b2, b1, b0) E, L, and G are each one bit Example: if A 010 and B 100, then the outputs would be: E-1, L-0 and G 1 (if active low outputs) Write this problem statement in the form of a truth table. There will be 6 columns for inputs and 3 columns for outputs. You could use K-maps to simplify the equations for E, L and G. How many variables would this K-map have? With Verilog you could skip the K-maps and design a solution based on a truth table and all the input possibilities. The "if-then-else if" Verilog construct would have 64 entries. A "case" construct would have 64 entries as well. Pick one or the other and design a Verilog solution. What kind of modeling technique is this called? With a good text editor you can copy, paste and edit changes rather quickly. Compile, download and test your "truth table" type of solution. Include your truth table, your Verilog source listing, and the test bench source in your lab report. Next after doing the above unsigned comparator, design your comparator to "interpret" the A and B numbers as "SIGNED" in twos complement format PART 5 - Design an unsigned 3-bit comparator such that "A" is compared to "B Inputs: A three bits (a2, a1, a0) Outputs: E A equal to B A less than B A greater than B B three bits (b2, b1, b0) E, L, and G are each one bit Example: if A 010 and B 100, then the outputs would be: E-1, L-0 and G 1 (if active low outputs) Write this problem statement in the form of a truth table. There will be 6 columns for inputs and 3 columns for outputs. You could use K-maps to simplify the equations for E, L and G. How many variables would this K-map have? With Verilog you could skip the K-maps and design a solution based on a truth table and all the input possibilities. The "if-then-else if" Verilog construct would have 64 entries. A "case" construct would have 64 entries as well. Pick one or the other and design a Verilog solution. What kind of modeling technique is this called? With a good text editor you can copy, paste and edit changes rather quickly. Compile, download and test your "truth table" type of solution. Include your truth table, your Verilog source listing, and the test bench source in your lab report. Next after doing the above unsigned comparator, design your comparator to "interpret" the A and B numbers as "SIGNED" in twos complement format

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts