Question: Need help with computer architecture problem. You have a byte-addressable virtual memory system with a two-entry TLB, a 2-way set associative cache and a page

Need help with computer architecture problem.

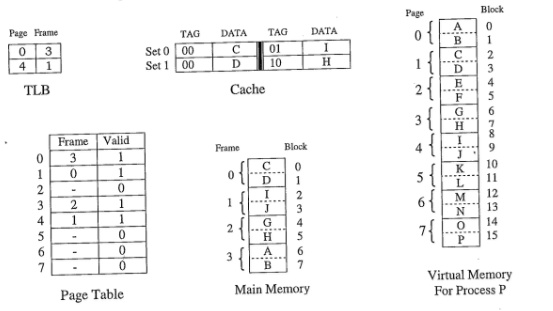

You have a byte-addressable virtual memory system with a two-entry TLB, a 2-way set associative cache and a page table for a process P. Assume cache blocks of 16 bytes and page size of 32 bytes. In the system below, main memory is divided up into blocks, where each block is represented by a letter. Two blocks equals one frame. See illustration below.

A. How many bits are required?

B. How many bits are required for physical address?

C. Show the address format for virtual address 1816 (specify field name and size) that would be used by the system to translate to a physical address and then translate the virtual address into the corresponding physical address. (Hint: convert 1816 to its binary equivalent and divide it into the appropriate fields.) Explain how these fields are used to translate to the corresponding physical address.

D. Given virtual address 6516

-What physical address does the virtual address 6516 maps to?

-Is this a TLB hit?

-Is the physical address above in the cache? If so, what is the set and tag?

E. Given virtual address 4516

-What page is the address in?

-What is the byte offset?

-Is the page in physical memory?

0123456789012345 012345 67 01234567 0 0123 Set lid-11-01-1000 30-21 1 01234567

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts