Question: Old MathJax webview (((Course: computer architecture))) The L2 data cache of a CPU is a 4KB, 2-Way Set Associative cache with 32-byte lines. The CPU

Old MathJax webview

(((Course: computer architecture)))

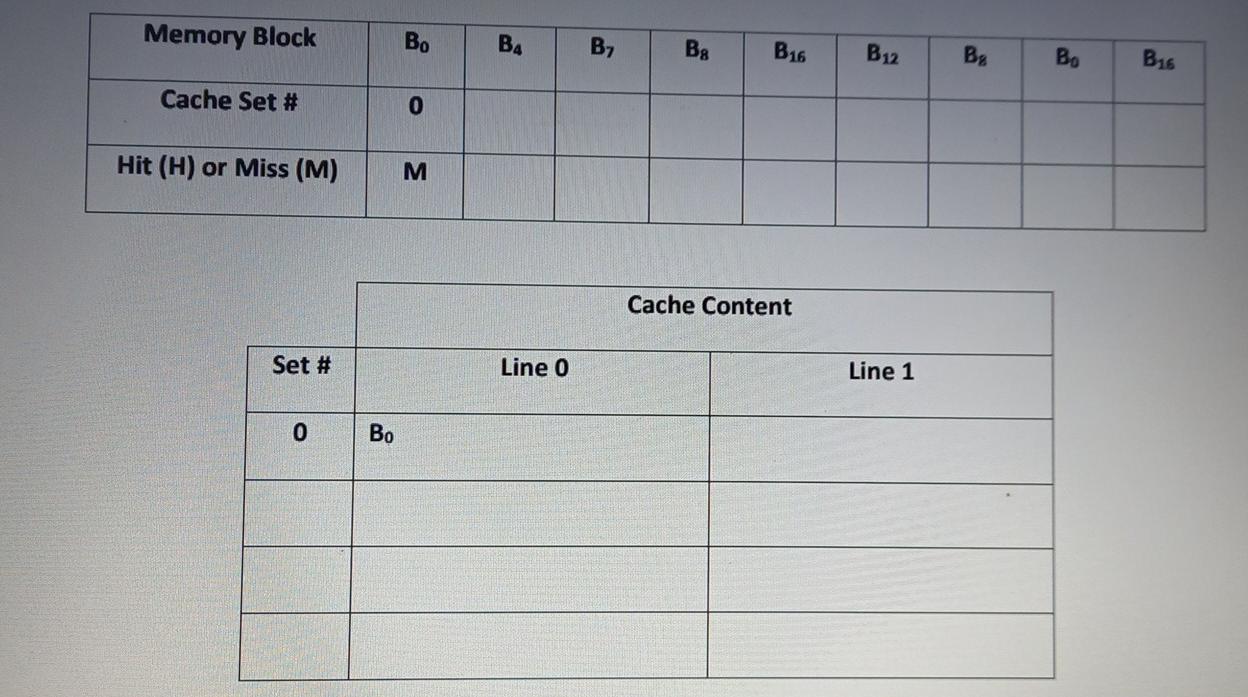

The L2 data cache of a CPU is a 4KB, 2-Way Set Associative cache with 32-byte lines. The CPU can address 8 MB of main memory.

1. What is the address mapping format (number of bits for TAG, SET, and WORD OFFSET).

2. Using LRU cache replacement rule, find if a miss or a hit occurs for the given sequence of CPU to memory address requests? Show the final content of the cache.

There is no missing information. Please solve this question without neglect..

Memory Block B2 Bg B16 B12 . Bo B15 Cache Set # 0 Hit (H) or Miss (M) M Cache Content Set # Line 0 Line 1 0

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts