Question: Please be quick QUESTION 1: Design a detector circuit with one input X and one output Y. Whenever the total number of ls received at

Please be quick

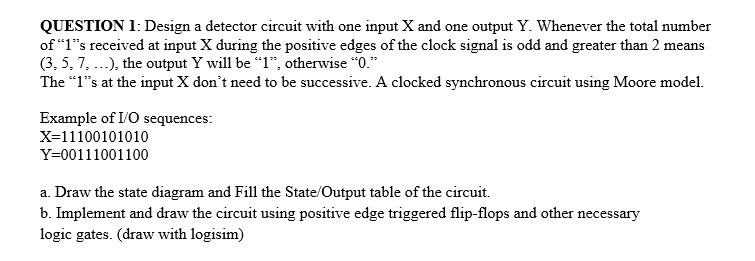

QUESTION 1: Design a detector circuit with one input X and one output Y. Whenever the total number of l"s received at input X during the positive edges of the clock signal is odd and greater than 2 means (3,5,7, ...), the output Y will be "1", otherwise "0." The "l's at the input X don't need to be successive. A clocked synchronous circuit using Moore model. Example of I/O sequences: X=11100101010 Y=00111001100 a. Draw the state diagram and Fill the State/Output table of the circuit. b. Implement and draw the circuit using positive edge triggered flip-flops and other necessary logic gates. (draw with logisim)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts