Question: Problem 3. Control and Data Hazards A benchmark in a five-stage pipelined processor has the following characteristics: 26% ALU instructions, 14% of these instructions are

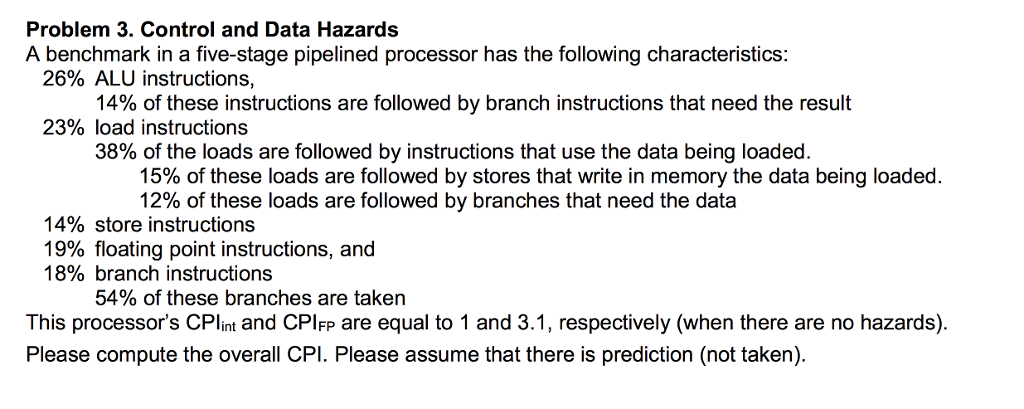

Problem 3. Control and Data Hazards A benchmark in a five-stage pipelined processor has the following characteristics: 26% ALU instructions, 14% of these instructions are followed by branch instructions that need the result 23% load instructions 38% of the loads are followed by instructions that use the data being loaded. 15% of these loads are followed by stores that write in memory the data being loaded. 12% of these loads are followed by branches that need the data 14% store instructions 19% floating point instructions, and 18% branch instructions 54% of these branches are taken This processor's CPlint and CPlFP are equal to 1 and 3.1, respectively (when there are no hazards). Please compute the overall CPl. Please assume that there is prediction (not taken). Problem 3. Control and Data Hazards A benchmark in a five-stage pipelined processor has the following characteristics: 26% ALU instructions, 14% of these instructions are followed by branch instructions that need the result 23% load instructions 38% of the loads are followed by instructions that use the data being loaded. 15% of these loads are followed by stores that write in memory the data being loaded. 12% of these loads are followed by branches that need the data 14% store instructions 19% floating point instructions, and 18% branch instructions 54% of these branches are taken This processor's CPlint and CPlFP are equal to 1 and 3.1, respectively (when there are no hazards). Please compute the overall CPl. Please assume that there is prediction (not taken)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts