Question: Problem 4 Cache Coherence Cache coherence concerns the views of multiple processors on a given cache block. The following table shows two processors and their

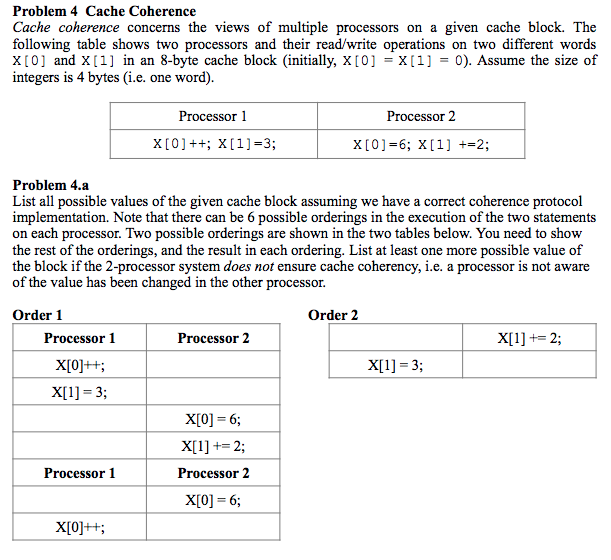

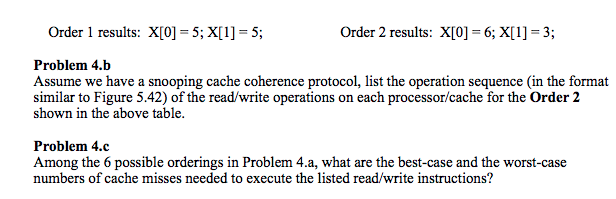

Problem 4 Cache Coherence Cache coherence concerns the views of multiple processors on a given cache block. The following table shows two processors and their read/write X[0] and X[1] in an 8-byte cache block (initially, X[0] -X[1] 0). Assume the size of integers is 4 bytes (i.e. one word) operations on two different words Processor1 Processor 2 Problem 4.a List all possible values of the given cache block assuming we have a correct coherence protocol implementation. Note that there can be 6 possible orderings in the execution of the two statements on each processor. Two possible orderings are shown in the two tables below. You need to show the rest of the orderings, and the result in each ordering. List at least one more possible value of the block if the 2-processor system does not ensure cache coherency, i.e. a processor is not aware of the value has been changed in the other processor. Order 1 Order 2 Processor 1 Processor 2 X1]+2; XI1]+ 2; Processor 1 Processor 2 Order l results: X[0]-5, X[1]-5; Order 2 results: xo-6 X-3; Problem 4.b Assume we have a snooping cache coherence protocol, list the operation sequence (in the format similar to Figure 5.42) of the read/write operations on each processor/cache for the Order 2 shown in the above table Problem 4.c Among the 6 possible orderings in Problem 4.a, what are the best-case and the worst-case numbers of cache misses needed to execute the listed read/write instructions? Problem 4 Cache Coherence Cache coherence concerns the views of multiple processors on a given cache block. The following table shows two processors and their read/write X[0] and X[1] in an 8-byte cache block (initially, X[0] -X[1] 0). Assume the size of integers is 4 bytes (i.e. one word) operations on two different words Processor1 Processor 2 Problem 4.a List all possible values of the given cache block assuming we have a correct coherence protocol implementation. Note that there can be 6 possible orderings in the execution of the two statements on each processor. Two possible orderings are shown in the two tables below. You need to show the rest of the orderings, and the result in each ordering. List at least one more possible value of the block if the 2-processor system does not ensure cache coherency, i.e. a processor is not aware of the value has been changed in the other processor. Order 1 Order 2 Processor 1 Processor 2 X1]+2; XI1]+ 2; Processor 1 Processor 2 Order l results: X[0]-5, X[1]-5; Order 2 results: xo-6 X-3; Problem 4.b Assume we have a snooping cache coherence protocol, list the operation sequence (in the format similar to Figure 5.42) of the read/write operations on each processor/cache for the Order 2 shown in the above table Problem 4.c Among the 6 possible orderings in Problem 4.a, what are the best-case and the worst-case numbers of cache misses needed to execute the listed read/write instructions

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts