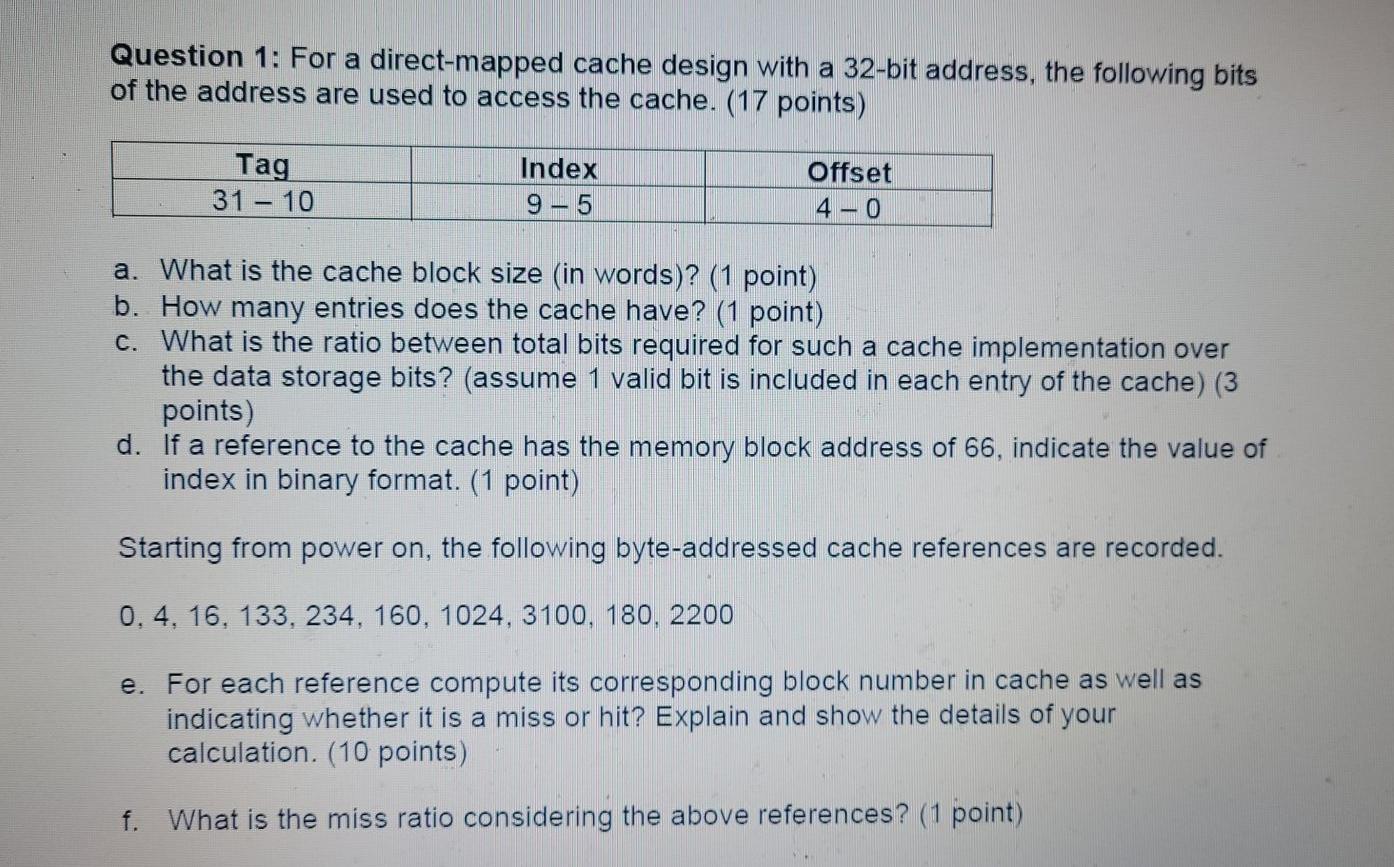

Question: Question 1: For a direct-mapped cache design with a 32-bit address, the following bits of the address are used to access the cache. (17 points)

Question 1: For a direct-mapped cache design with a 32-bit address, the following bits of the address are used to access the cache. (17 points) Tag 31 10 Index 9-5 Offset 4-0 a. What is the cache block size (in words)? (1 point) b. How many entries does the cache have? (1 point) c. What is the ratio between total bits required for such a cache implementation over the data storage bits? (assume 1 valid bit is included in each entry of the cache) (3 points) d. If a reference to the cache has the memory block address of 66, indicate the value of index in binary format. (1 point) Starting from power on, the following byte-addressed cache references are recorded. 0, 4, 16, 133, 234, 160, 1024, 3100, 180, 2200 e. For each reference compute its corresponding block number in cache as well as indicating whether it is a miss or hit? Explain and show the details of your calculation. (10 points) f. What is the miss ratio considering the above references? (1 point)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts