Question: Question 3: Suppose we have a cache and main memory, connected with a 32 bit data bus. A hit in the cache takes one clock

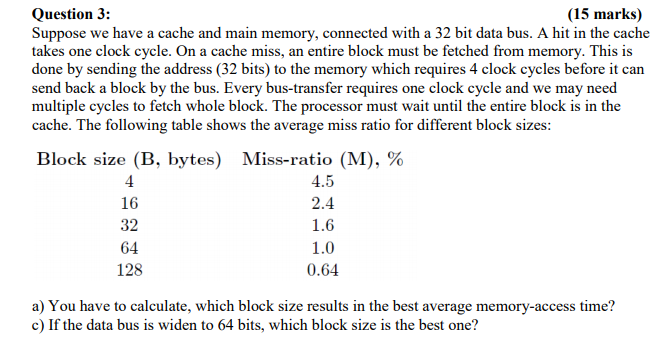

Question 3: Suppose we have a cache and main memory, connected with a 32 bit data bus. A hit in the cache takes one clock cycle. On a cache miss, an entire block must be fetched from memory. This is done by sending the address (32 bits) to the memory which requires 4 clock cycles before it can (15 marks) send back a block by the bus. Every bus-transfer requires one clock cycle and we may need multiple cycles to fetch whole block. The processor must wait until the entire block is in the cache. The following table shows the average miss ratio for different block sizes: Miss-ratio (M), % 4.5 2.4 1.6 1.0 0.64 Block size (B, bytes) 16 32 64 128 a) You have to calculate, which block size results in the best average memory-access time? c) If the data bus is widen to 64 bits, which block size is the best one? Question 3: Suppose we have a cache and main memory, connected with a 32 bit data bus. A hit in the cache takes one clock cycle. On a cache miss, an entire block must be fetched from memory. This is done by sending the address (32 bits) to the memory which requires 4 clock cycles before it can (15 marks) send back a block by the bus. Every bus-transfer requires one clock cycle and we may need multiple cycles to fetch whole block. The processor must wait until the entire block is in the cache. The following table shows the average miss ratio for different block sizes: Miss-ratio (M), % 4.5 2.4 1.6 1.0 0.64 Block size (B, bytes) 16 32 64 128 a) You have to calculate, which block size results in the best average memory-access time? c) If the data bus is widen to 64 bits, which block size is the best one

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts