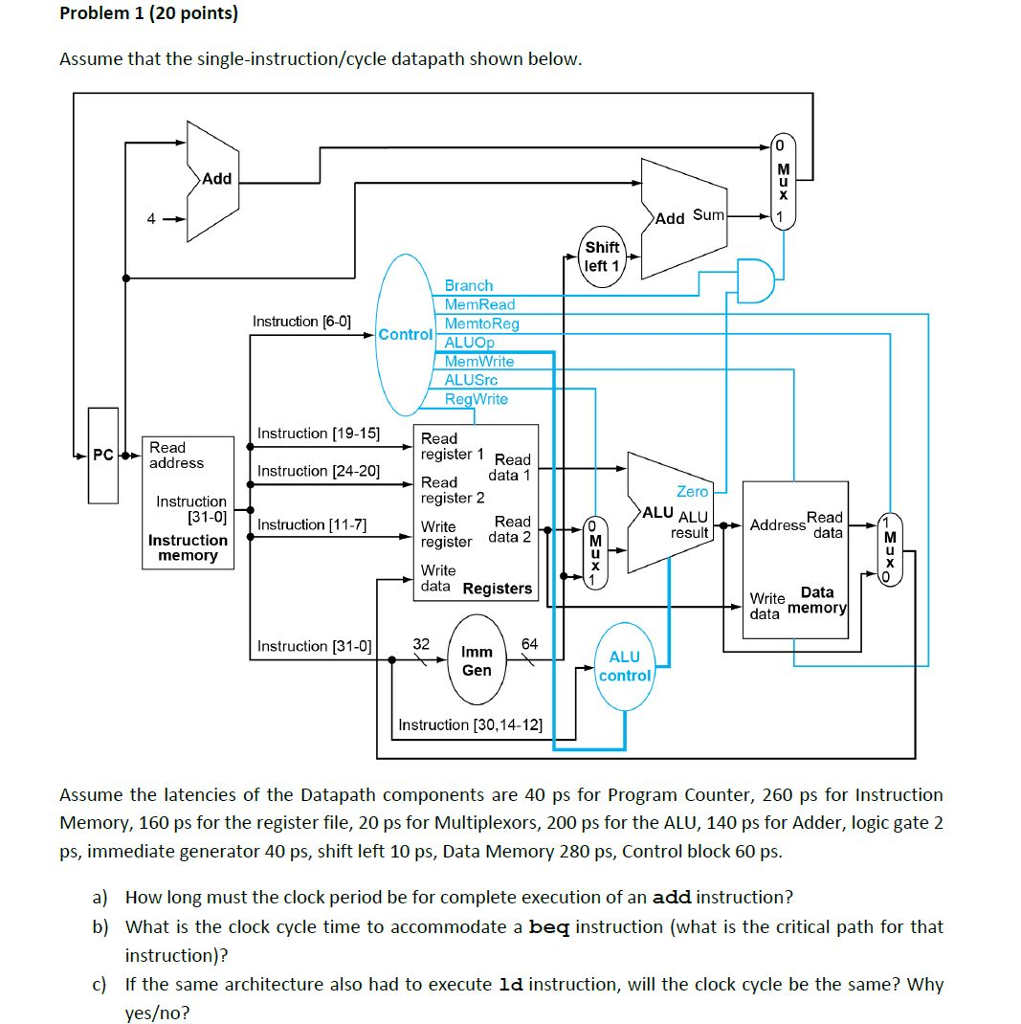

Question: RISC-V ASSEMBLY LANGUAGE Problem 1 (20 points) Assume that the single-instruction/cycle datapath shown below 0 Add 4. Add Sunm Shift left 1 Branch MemRead MemtoRe

RISC-V ASSEMBLY LANGUAGE

Problem 1 (20 points) Assume that the single-instruction/cycle datapath shown below 0 Add 4. Add Sunm Shift left 1 Branch MemRead MemtoRe Instruction [6-0] Control ALUOP MemWrite ALUSrc RegWrite Instruction [19-15Read Read address register 1 Read Read register 2 Write Read register data 2 Write data Registers PC Instruction [24-20] data 1 Zero ALU ALU result Instruction 31-0nstruction [11-7] AddressRead data Instruction memory Write Data data memor Instruction [31-011 32. Imm ) 4 Gen ALU control Instruction [30,14-12] Assume the latencies of the Datapath components are 40 ps for Program Counter, 260 ps for Instruction Memory, 160 ps for the register file, 20 ps for Multiplexors, 200 ps for the ALU, 140 ps for Adder, logic gate 2 ps, immediate generator 40 ps, shift left 10 ps, Data Memory 280 ps, Control block 60 ps a) How long must the clock period be for complete execution of an add instruction? b) What is the clock cycle time to accommodate a beq instruction (what is the critical path for that instruction)? If the same architecture also had to execute ld instruction, will the clock cycle be the same? Why yeso? c)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts