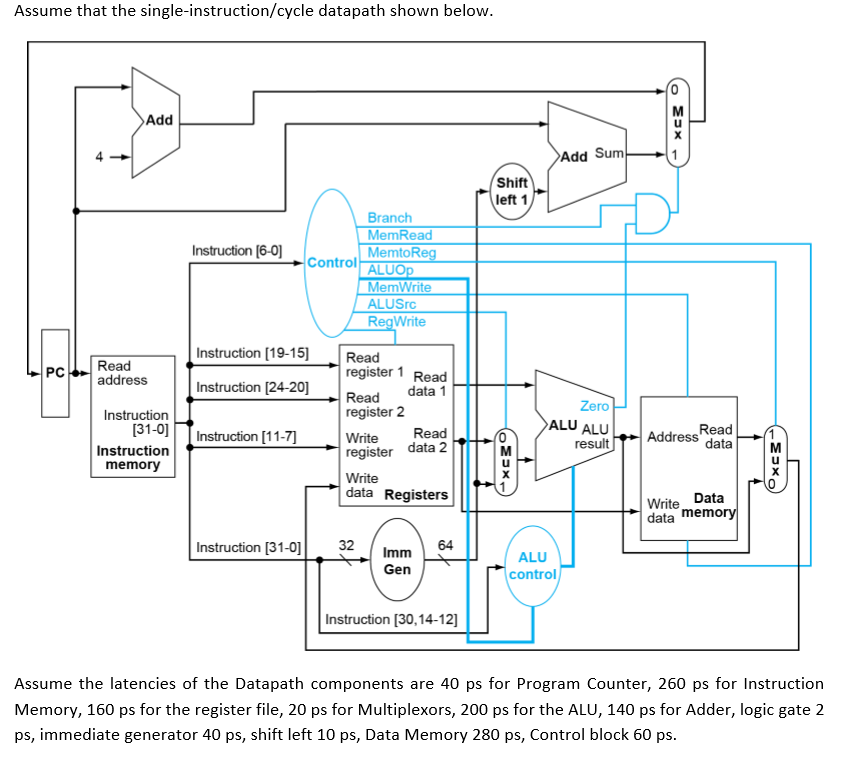

Question: Assume that the single-instruction/cycle datapath shown below Add 4 Add Sum Shift left 1 Branch MemRead MemtoR Instruction bControl ALU [6-0] MemWrite ALUSrc RegWrite Instruction

![Shift left 1 Branch MemRead MemtoR Instruction bControl ALU [6-0] MemWrite ALUSrc](https://dsd5zvtm8ll6.cloudfront.net/si.experts.images/questions/2024/09/66f450c39d548_49166f450c34a5f5.jpg)

Assume that the single-instruction/cycle datapath shown below Add 4 Add Sum Shift left 1 Branch MemRead MemtoR Instruction bControl ALU [6-0] MemWrite ALUSrc RegWrite Instruction [19-15 Read Read PCaddress register 1 Read Instruction [24-20] Read data 1 register 2 Zero Instruction 131-01 Instruction [1-7 Write Read register data 2 resultAddress Read Instruction memory Ul data Registers Write Data data memo Imm64 Gen Instruction [31-0 32 ALU control Instruction [30,14-12 Assume the latencies of the Datapath components are 40 ps for Program Counter, 260 ps for Instruction Memory, 160 ps for the register file, 20 ps for Multiplexors, 200 ps for the ALU, 140 ps for Adder, logic gate 2 ps, immediate generator 40 ps, shift left 10 ps, Data Memory 280 ps, Control block 60 ps

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts