Question: Suppose the DLX architecture is modified such that each instructions excursions takes 8 clock cycles, where the ALU is slow and the execute phase needs

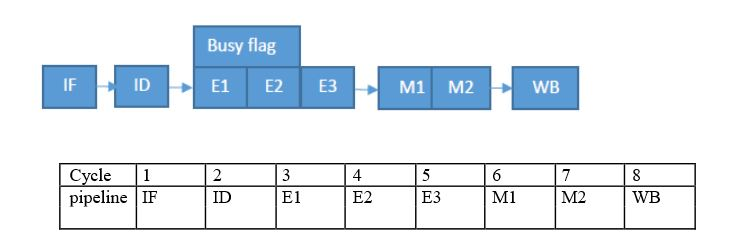

Suppose the DLX architecture is modified such that each instructions excursions takes 8 clock cycles, where the ALU is slow and the execute phase needs more 3 clock cycles ( E1, E2, and E3) and data memory takes 2 cycles (M1 and M2), if the ALU is not internally pipelined ( i.e only one instruction can use the ALU), memory is not always pipelined ( i.e only one instruction can access memory) :

1. Assume forwarding exists in DLX, Write the number of clock cycles needed, and any stall required. For all parts, indicate the comparator needed to detect forwarding or stall if exists.

2. Assume that if the ALU is internally pipelined (there could be more than one instruction at a time in the ALU, Repeat problem 6 with the above 8 stages pipeline.

Busy flag E1 E2 E3 WB M1 M2 Cycle 1 2 3 4 6 7 pipeline IF E1 ID E3 M2

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts