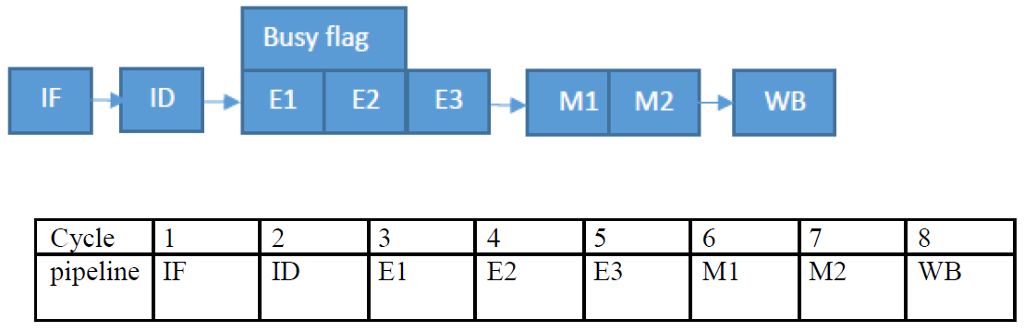

Question: Suppose the DLX architecture is modified such that each instructions excursions takes 8 clock cycles, where the ALU is slow and the execute phase needs

Suppose the DLX architecture is modified such that each instructions excursions takes 8 clock cycles, where the ALU is slow and the execute phase needs more 3 clock cycles ( E1, E2, and E3) and data memory takes 2 cycles (M1 and M2), if the ALU is not internally pipelined ( i.e only one instruction can use the ALU), memory is not always pipelined ( i.e only one instruction can access memory) :

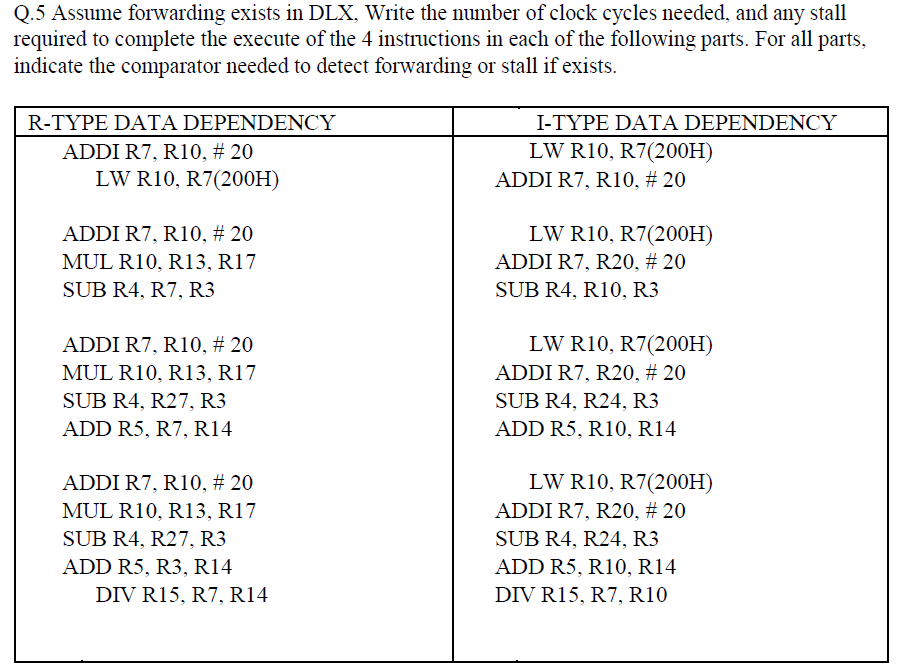

1) Repeat problem 5 with the above 8 stages pipeline PROBLEM 5:

2) Assume that if the ALU is internally pipelined (there could be more than one instruction at a time in the ALU, Repeat problem 6 with the above 8 stages pipeline.

Q.6 Show the logic that is needed to: 1- Detect if a register contains all zeros. 2- Detect if the value in two registers are equal or not.

Busy flag E1 E2 E3 M1 M2 WB Cycle 1 3 4 L5 7 pipeline IF E2 E3 M1 WB

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts