Question: Use FSM state diagram and code. Use even binary. 1. (A)Draw a state diagram below for a 3-bit binary even number up counter with a

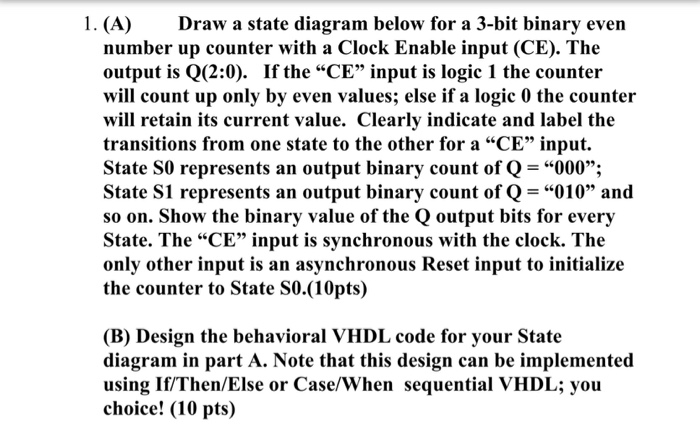

1. (A)Draw a state diagram below for a 3-bit binary even number up counter with a Clock Enable input (CE). The output is Q(2:0). If the "CE" input is logic 1 the counter will count up only by even values; else if a logic 0 the counter will retain its current value. Clearly indicate and label the transitions from one state to the other for a CE input. State S0 represents an output binary count of Q = 000". State S1 represents an output binary count of Q-010" and so on. Show the binary value of the Q output bits for every State. The CE input is synchronous with the clock. The only other input is an asynchronous Reset input to initialize the counter to State S0.(10pts) (B) Design the behavioral VHDL code for your State diagram in part A. Note that this design can be implemented using If/Then/Else or Case/When sequential VHDL; you choice! (10 pts)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts