Question: verilog code please Behavioural Four Button Lock The following lock is unlocked with the sequence B3, B1, B2, and BO. Implement the four button lock

verilog code please

verilog code please

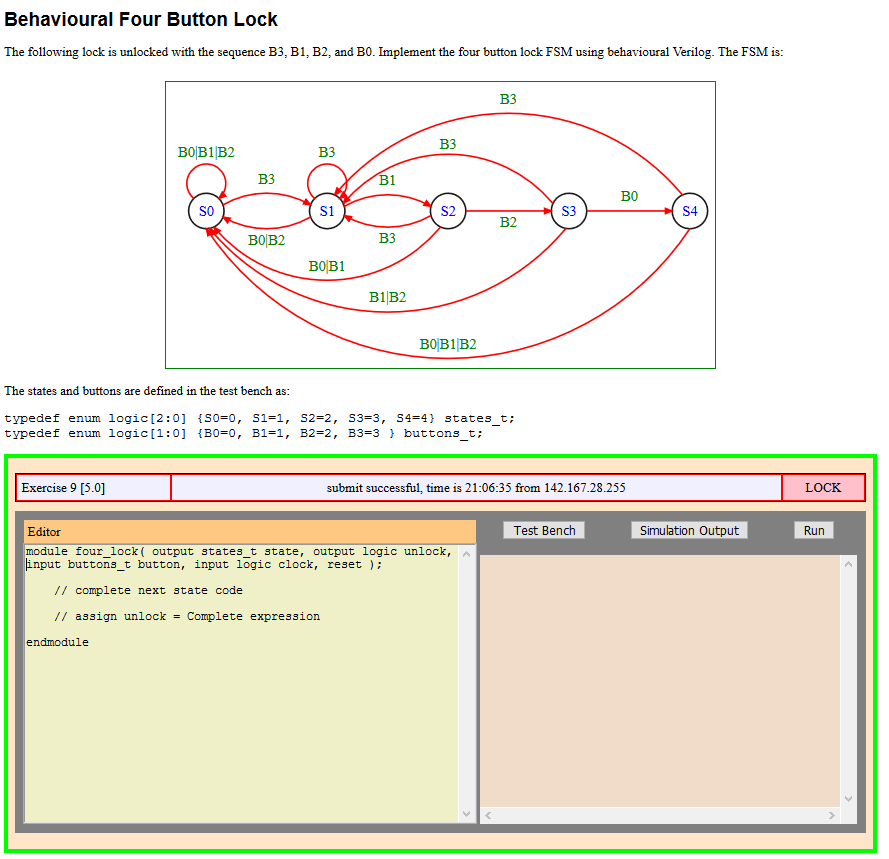

Behavioural Four Button Lock The following lock is unlocked with the sequence B3, B1, B2, and BO. Implement the four button lock FSM using behavioural Verilog. The FSM is: B3 B3 B0B1/B2 B3 B3 B1 BO SO S1 S2 S3 S4 B2 BOB2 B3 BOB1 B1/B2 BOB1B2 The states and buttons are defined in the test bench as: typedef enum logic[2:0] {S0=0, 51=1, 52=2, S3=3, S4=4} states_t; typedef enum logic[1:0] {B0=0, B1=1, B2=2, B3=3 } buttons_t; Exercise 9 [5.0] submit successful, time is 21:06:35 from 142.167.28.255 LOCK Test Bench Simulation Output Run Editor module four_lock ( output states_t state, output logic unlock, input buttons_t button, input logic clock, reset ); // complete next state code // assign unlock - Complete expression endmodule Behavioural Four Button Lock The following lock is unlocked with the sequence B3, B1, B2, and BO. Implement the four button lock FSM using behavioural Verilog. The FSM is: B3 B3 B0B1/B2 B3 B3 B1 BO SO S1 S2 S3 S4 B2 BOB2 B3 BOB1 B1/B2 BOB1B2 The states and buttons are defined in the test bench as: typedef enum logic[2:0] {S0=0, 51=1, 52=2, S3=3, S4=4} states_t; typedef enum logic[1:0] {B0=0, B1=1, B2=2, B3=3 } buttons_t; Exercise 9 [5.0] submit successful, time is 21:06:35 from 142.167.28.255 LOCK Test Bench Simulation Output Run Editor module four_lock ( output states_t state, output logic unlock, input buttons_t button, input logic clock, reset ); // complete next state code // assign unlock - Complete expression endmodule

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts