Question: Verilog code Please edit Convert.v and test_convert.v codes .. and wirte a code here. thanks Aim: Design a serial BCD to Excess-3 code converter by

Verilog code

Please edit Convert.v and test_convert.v codes .. and wirte a code here. thanks

Aim: Design a serial BCD to Excess-3 code converter by using Verilog.

Description:

Use Verilog to design a circuit that accepts serially 4 bits representing a BCD digit and outputs serially the corresponding Excess-3 representation.

Steps:

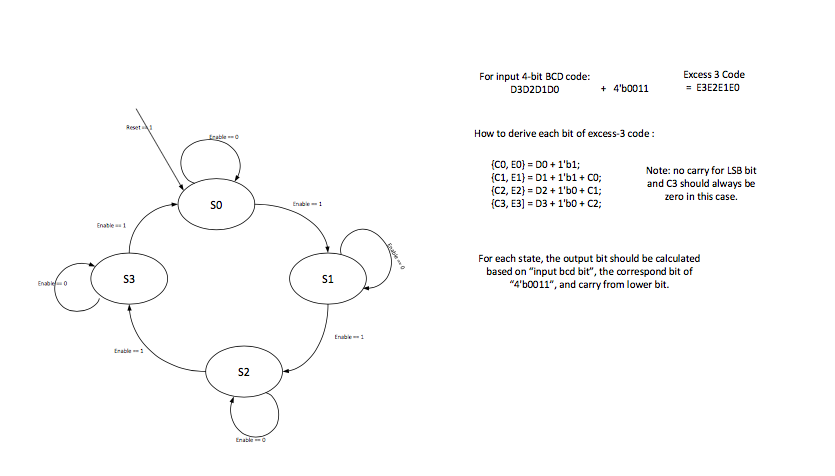

1. Obtain the state diagram as shown in class.

2. Write the verilog code that implements that state diagram, using the synchronous FSM template given in class. You need to fill in some places based on your understanding.

3. Simulate your design with given testbench by VCS.

Converter.v

module Converter( input clk , input reset , input di , input enable , output reg do );

reg [2:0] c_state ; reg [2:0] n_state ;

parameter S0 = 3'b000; parameter S1 = 3'b001; parameter S2 = 3'b011; parameter S3 = 3'b010;

reg carry ;

//Define output always@(*)begin case(c_state) S0: do = ~di ; S1: do = ~(di^carry) ; S2: do = place your code here S3: do = place your code here default:do = 1'b0 ; endcase end

//Carry for next bit always@(posedge clk or negedge reset)begin if(reset) carry

//Define n_state always@(*)begin case(c_state) S0: if(enable) //waiting for LSB n_state = S1 ; else n_state = S0 ; S1: if(enable) //waiting for second lowest bit n_state = S2 ; else n_state = S1 ; S2: if(enable) place your code here ; else place your code here ; S3: if(enable) place your code here ; else place your code here ; default: n_state = S0 ; endcase end

always@(posedge clk or posedge reset)begin if(reset) c_state

endmodule

test_converter.v

module test_converter(); reg clk ; reg reset ;

reg enable ; reg di ; wire do ;

reg [3:0] bcd ; reg [2:0] clk_cnt ; reg [3:0] excess3 ;

initial begin #10 clk = 1'b0 ; reset = 1'b0 ; enable = 1'b0 ; di = 1'b0 ; #100 reset = 1'b1 ; #47 reset = 1'b0 ; #50000 $finish ; end

always #5 clk

always@(posedge clk or posedge reset)begin if(reset) clk_cnt

//BCD change as stimulus always@(posedge clk or posedge reset)begin if(reset) bcd

always@(posedge clk or posedge reset)begin if(reset) enable

always@(*)begin case(clk_cnt) 3'd1: di = bcd[0] ; 3'd2: di = bcd[1] ; 3'd3: di = bcd[2] ; 3'd4: di = bcd[3] ; default: di = 1'b0 ; endcase end

always@(posedge clk or posedge reset)begin if(reset) excess3

Converter u_converter( .clk (clk ), .reset (reset ), .enable (enable ), .di (di ), .do (do ) );

endmodule

Please edit Convert.v and test_convert.v codes .. and wirte a code here. thanks

S3 Excess 3 Code For input it BCD code: 4b0011 E3E2E1EO D3D2D1DO How to derive each bit of excess-3 code: (CO, DO 1'bl; Note: no carry for LSB bit (C1, E1)- D1 1'bl CO; and C3 should always be (C2, E2) D2 1'b0 C1; zero in this case. C3, E3 D3 1'b0 C2 For each state, the output bit should be calculated based on "input bcd bit", the correspond bit of W4'bo011", and carry from lower bit. S3 Excess 3 Code For input it BCD code: 4b0011 E3E2E1EO D3D2D1DO How to derive each bit of excess-3 code: (CO, DO 1'bl; Note: no carry for LSB bit (C1, E1)- D1 1'bl CO; and C3 should always be (C2, E2) D2 1'b0 C1; zero in this case. C3, E3 D3 1'b0 C2 For each state, the output bit should be calculated based on "input bcd bit", the correspond bit of W4'bo011", and carry from lower bit

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts