Question: Verilog Code Verilog Code Verilog Code Verilog Code Verilog Code Verilog Code Verilog Code Verilog Code Need to build up a Droplet like system. Details

Verilog Code Verilog Code Verilog Code Verilog Code Verilog Code Verilog Code Verilog Code Verilog Code

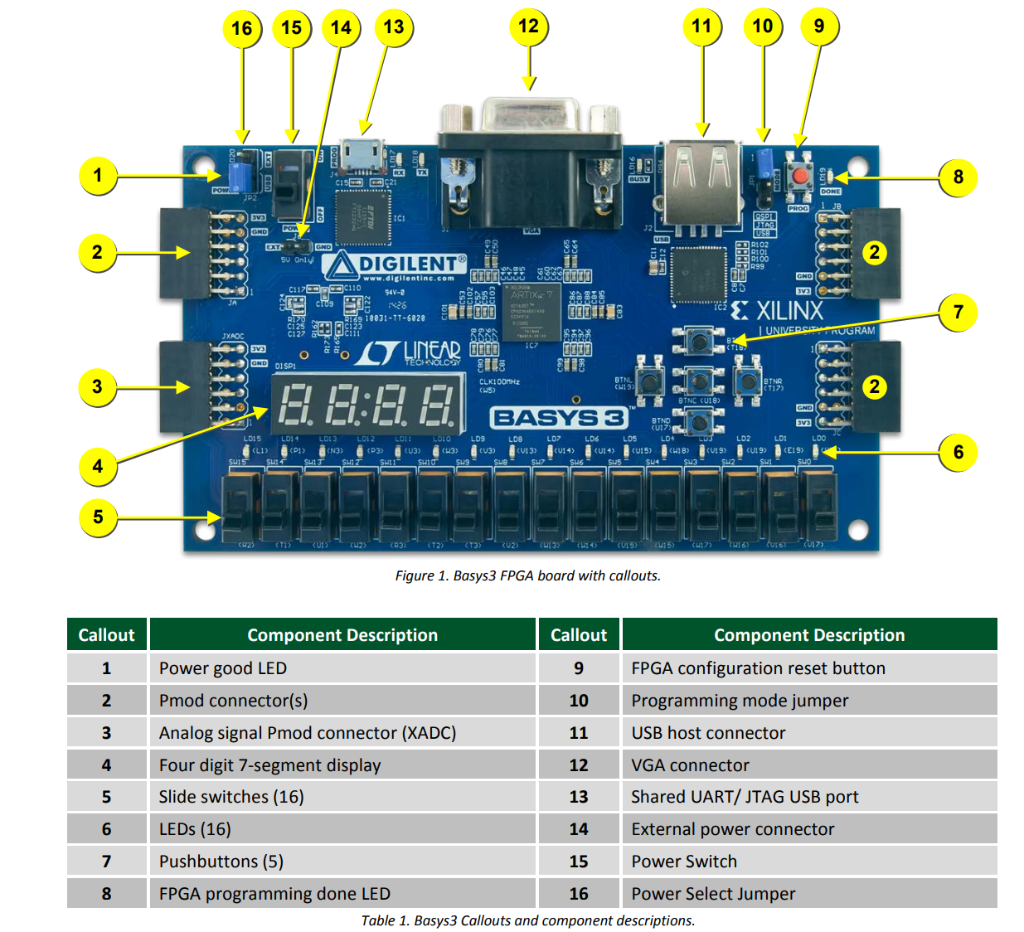

Need to build up a Droplet like system. Details in pictures. Basys3 Artix-7 FPGA Board

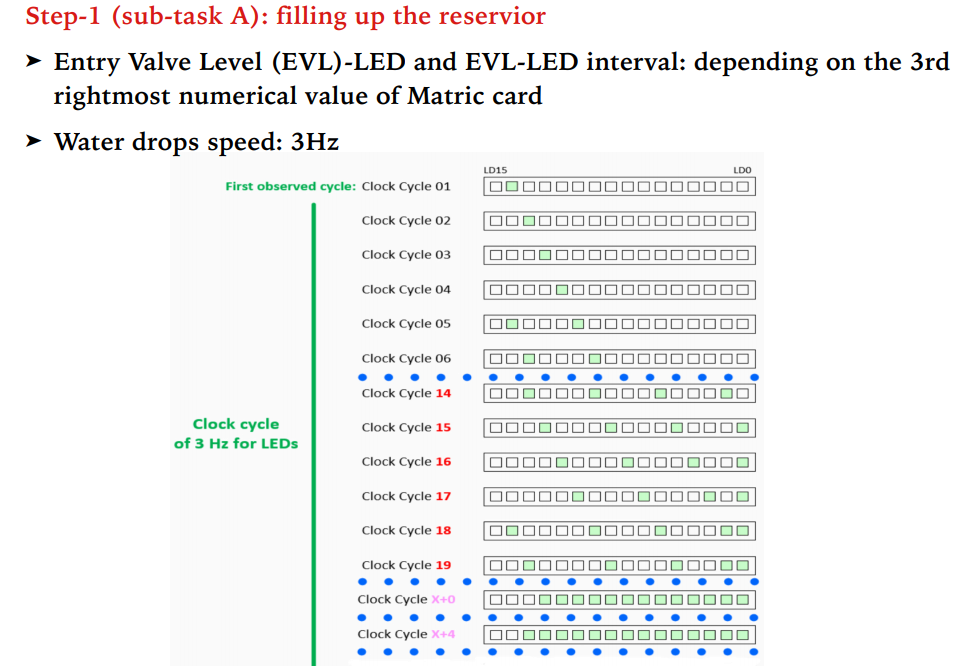

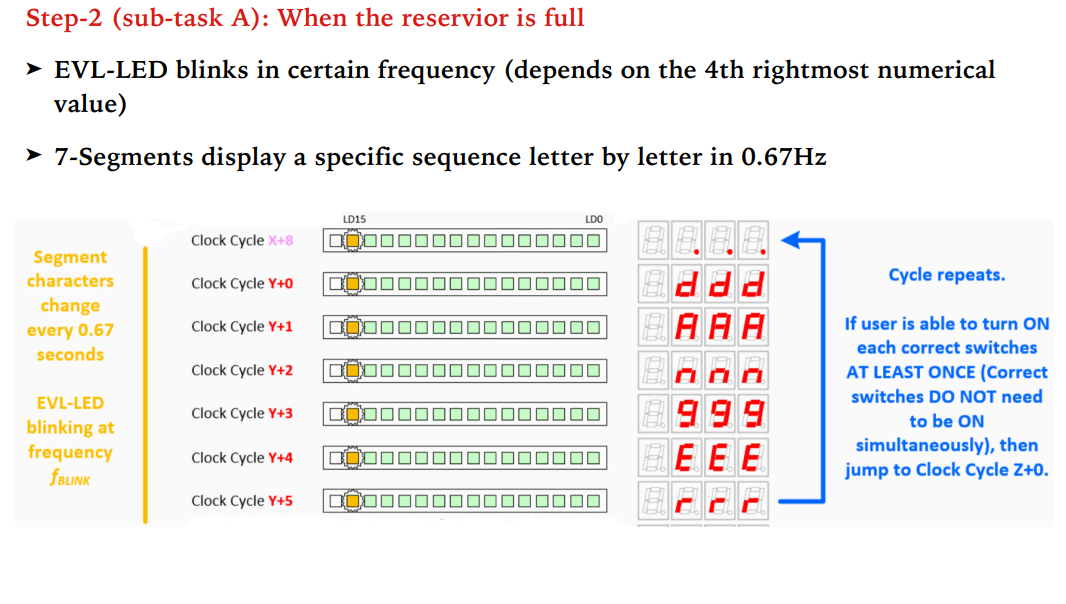

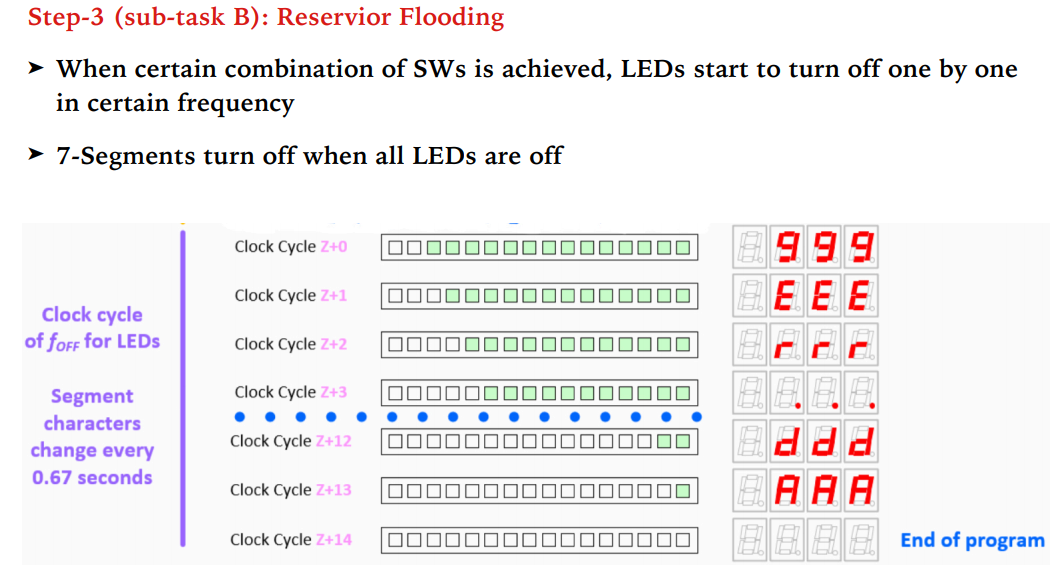

The rightmost 3 seven-segment displays out of the 4 seven-segment displays will be ON wherever required during the running of the program The EVL is 14, and the EVL-LED is LD14. A new drop of water (New LED light up at EVL-LED) appears every 1.33 seconds Water is discharged from the water reservoir at a frequency foFF = 3.00 Hz (One LEDs turn OFF every 0.33 seconds) The characters to appear sequentially on the activated seven segment displays are: . DANGER). DANGER. D... To discharge water when the reservoir is full, the correct switches that must be turned ON or were previously ON are: SW2, SW8, SW13 Step-1 (sub-task A): filling up the reservior Entry Valve Level (EVL)-LED and EVL-LED interval: depending on the 3rd rightmost numerical value of Matric card Water drops speed: 3Hz First observed cycle: Clock Cycle 01 LD15 LDO [ DDDDDDDDDDDDDDDD Clock Cycle 02 JOO 00 Clock Cycle 03 Clock Cycle 04 OD Clock Cycle 05 DO OOOOOO DON JU Clock Cycle 06 . Clock Cycle 14 O C DOOD DDDDDDDD Clock Cycle 15 DODDDDDDDDDDDDDD Clock cycle of 3 Hz for LEDs 3 Clock Cycle 16 DDDDDDDDDDD Clock Cycle 17 000000 DOD Clock Cycle 18 Clock Cycle 19 OOO OD O Clock Cycle X+0 . . Clock Cycle X+4 . NNNN Step-2 (sub-task A): When the reservior is full > EVL-LED blinks in certain frequency (depends on the 4th rightmost numerical value) > 7-Segments display a specific sequence letter by letter in 0.67Hz LD15 LDO Clock Cycle X+8 EHE Clock Cycle Y+0 DOC Cycle repeats. Segment characters change every 0.67 seconds D D A A A Clock Cycle Y+1 Clock Cycle Y+2 ann Clock Cycle Y+3 If user is able to turn ON each correct switches AT LEAST ONCE (Correct switches DO NOT need to be ON simultaneously), then jump to Clock Cycle Z+0. EVL-LED blinking at frequency fBLINK DO 999 E E E Clock Cycle Y+4 DOD Clock Cycle Y+5 Step-3 (sub-task B): Reservior Flooding When certain combination of SWs is achieved, LEDs start to turn off one by one in certain frequency 7-Segments turn off when all LEDs are off Clock Cycle Z+0 DO 999 E EE Clock Cycle 2+1 Clock cycle of foff for LEDs Clock Cycle 2+2 Clock Cycle 2+3 Segment characters change every 0.67 seconds Clock Cycle 2+12 a da A A A Clock Cycle Z+13 ON Clock Cycle 2+14 End of program 646564 16 15 14 13 12 11 10 9 1 RETS BUSY 8 POW DONE JP2 PROG SOT TAG USE 102 A101 R100 98 2 2 V3 TCI GND PO EXT GND su Only www.digilenting.com CHOCH10 94V-2 KON 26 RP 19031-TT-5028 C128 ORE C127 SC Weili ADIGILENT GOCESSUS ESCOLE GND sve ARTIX-7 3336 TO 11000 C XILINX 7 | UNIVERSITERUGRAM JXAOC 1c7 0033 O O GND DISPL LINEAR DOEL TECHNOLOGY 6. CLKIOMI 3 BTN CHIS BTN (117) 2 88:8.8. BASYS BTNC (U10) GND EVE LOIS LD14 LOI3 LOI2 LD: LOIO LDS

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts