Question: Verilog Example 1 ` ` ` always @ ( posedge CLK ) if ( S 1 ) then R 1 = R 1 + R

Verilog Example

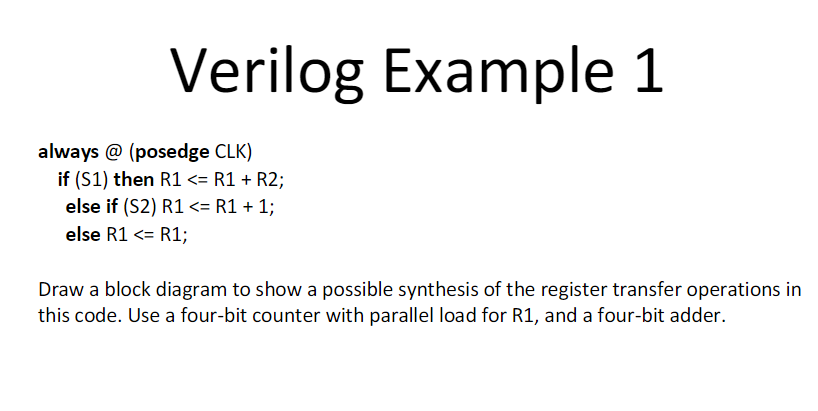

always @ posedge CLK

if S then R R R;

else if S R R;

else R R;

Draw a block diagram to show a possible synthesis of the register transfer operations in this code. Use a fourbit counter with parallel load for R and a fourbit adder.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock