Question: We have a 5-stage pipeline processor (F, ID, EX, MEM, WB). Consider the following piece of code: l1: sw $16, 10($6) l2: lw $4, 18($16)

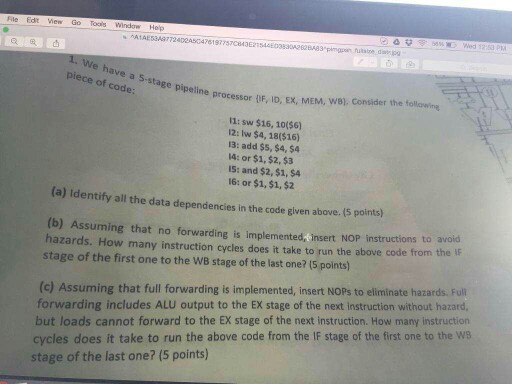

We have a 5-stage pipeline processor (F, ID, EX, MEM, WB). Consider the following piece of code: l1: sw $16, 10($6) l2: lw $4, 18($16) l3: add $5, $4, $4 l4: or $1, $2, $3 l5: and $2, $1, $4 l6: or $1, $1, $2 (a) Identify all the data dependencies in the code given above. (b) Assuming that no forwarding is implemented, insert NOP instructions to avoid hazards. How forwarding does it take to run the above code from the IF many instruction cycles stage of the first one to the WB stage of the last one? (c) Assuming that full forwarding is implemented, insert NOPs to eliminate hazards. Full forwarding includes ALU output to the Ex stage of the next instruction without hazard, but loads cannot forward to the EX stage of the next instruction. How many instruction cycles does it take to run the above code from the IF stage of the first one to the WB stage of the last one? We have a 5-stage pipeline processor (F, ID, EX, MEM, WB). Consider the following piece of code: l1: sw $16, 10($6) l2: lw $4, 18($16) l3: add $5, $4, $4 l4: or $1, $2, $3 l5: and $2, $1, $4 l6: or $1, $1, $2 (a) Identify all the data dependencies in the code given above. (b) Assuming that no forwarding is implemented, insert NOP instructions to avoid hazards. How forwarding does it take to run the above code from the IF many instruction cycles stage of the first one to the WB stage of the last one? (c) Assuming that full forwarding is implemented, insert NOPs to eliminate hazards. Full forwarding includes ALU output to the Ex stage of the next instruction without hazard, but loads cannot forward to the EX stage of the next instruction. How many instruction cycles does it take to run the above code from the IF stage of the first one to the WB stage of the last one

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts