Question: When processor designers consider a possible improvement to the processor datapath, the decision usually depends on the cost/performance trade-off. In the following problems, assume that

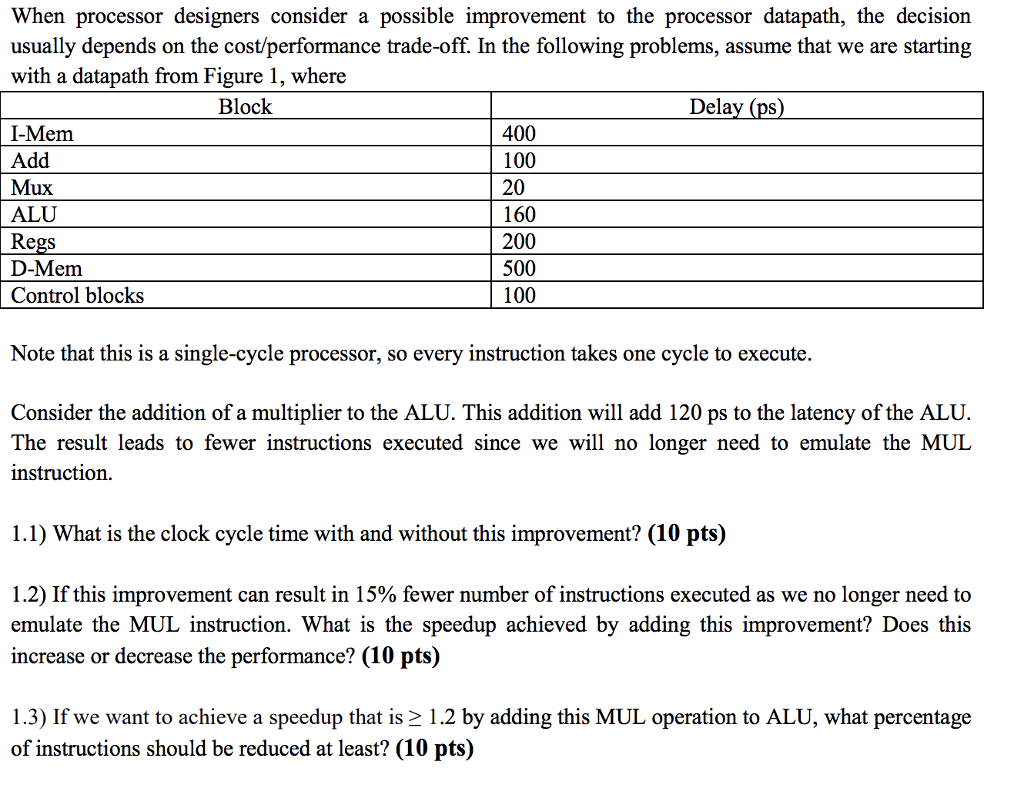

When processor designers consider a possible improvement to the processor datapath, the decision usually depends on the cost/performance trade-off. In the following problems, assume that we are starting with a datapath from Figure 1, where Block Delay (ps I-Mem Add Mux ALU Regs 400 100 20 160 200 500 100 D-Mem Control blocks Note that this is a single-cycle processor, so every instruction takes one cycle to execute Consider the addition of a multiplier to the ALU. This addition will add 120 ps to the latency of the ALU The result leads to fewer instructions executed since we will no longer need to emulate the MUL instruction. 1.1) What is the clock cycle time with and without this improvement? (10 pts) 1.2) If this improvement can result in 15% fewer number of instructions executed as we no longer need to emulate the MUL instruction. What is the speedup achieved by adding this improvement? Does this increase or decrease the performance? (10 pts) 1.3) If we want to achieve a speedup that is 2 1.2 by adding this MUL operation to ALU, what percentage of instructions should be reduced at least? (10 pts)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts