Question: Write a test-bench program. Cover all input combinations in binary incrementing order. library IEEE use IEEE.std. logic.1164.a11 library unisin; use unisim.vcomponents.al1; entity prime is ort

Write a test-bench program. Cover all input combinations in binary incrementing order.

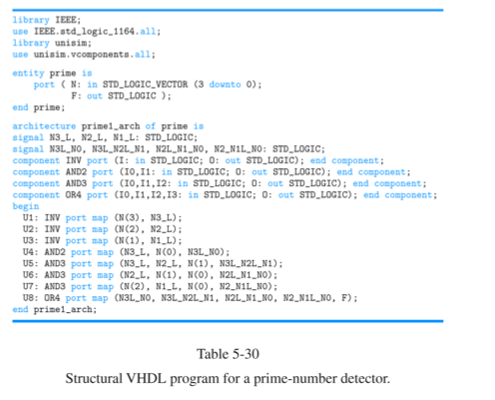

library IEEE use IEEE.std. logic.1164.a11 library unisin; use unisim.vcomponents.al1; entity prime is ort N:in STD LOGIC VECTOR (3 downto 0) F: out STD LOGIC end prise architecture prime1 arch of prine is signal N3L, N2.L, N1.L: STD LOGIC component INV port (I: in STD LOGIC; 0: out STD LOGIC): end component component AND2 port CIO,I1: in STD.LOGIC: 0: out STD LOGIC): end component component AND3 port (IO,I1,12: in STD LOGIC: O: out STD LOGIC); end component component OR4 port (O,I1.12,13: in STD LOGIC: 0: out STD LOGIC): end component begin U1: INV port map N(3), N3 L) U2: INV port map NC2). N2.L) U3: INV port map (N(1), 1-L); U4: AND2 port map (N3L, NO)NLNO): US: AND3 port map (N3L, N2L, N1),N3L N2L N1) U6: AND3 port map CN2.L, NI),NCO). N2L N1NO); U7: AND3 port map CNC2), NL, NO), N2 N1L NO); U8: OR4 port map CN3LNO, N3L N2LN1, N2L N1 NO, N2.NIL NO. F) end prine1 arch; Table 5-30 Structural VHDL program for a prime-number detector

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts