Question: Write VHDL Code: Design a 4-bit binary counter with asynchronous reset using behavioral implementation style. The component starts counting if Count_Enable signal is 1, otherwise

Write VHDL Code:

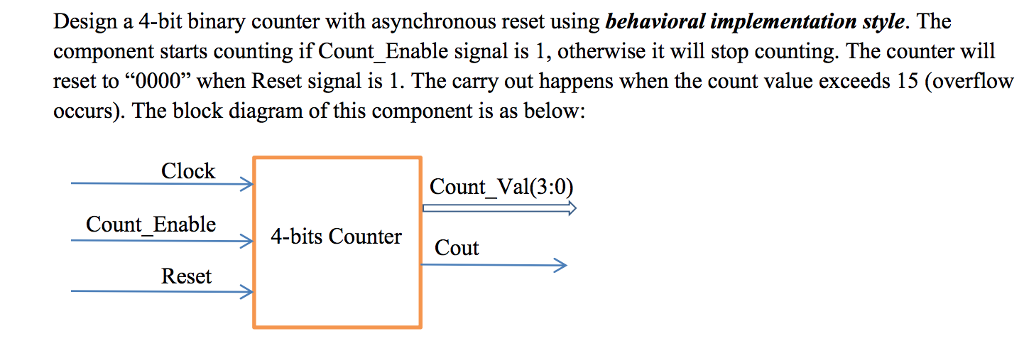

Design a 4-bit binary counter with asynchronous reset using behavioral implementation style. The component starts counting if Count_Enable signal is 1, otherwise it will stop counting. The counter will reset to "0000" when Reset signal is 1. The carry out happens when the count value exceeds 15 (overflow occurs). The block diagram of this component is as below: Clock> Count_Val(3:0) Count Enable 4-bits Counter Cout Reset >

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts