Question: You are building a system around a single-issue in-order processor running at 1 GHz and the processor has a base CPI of1 if all memory

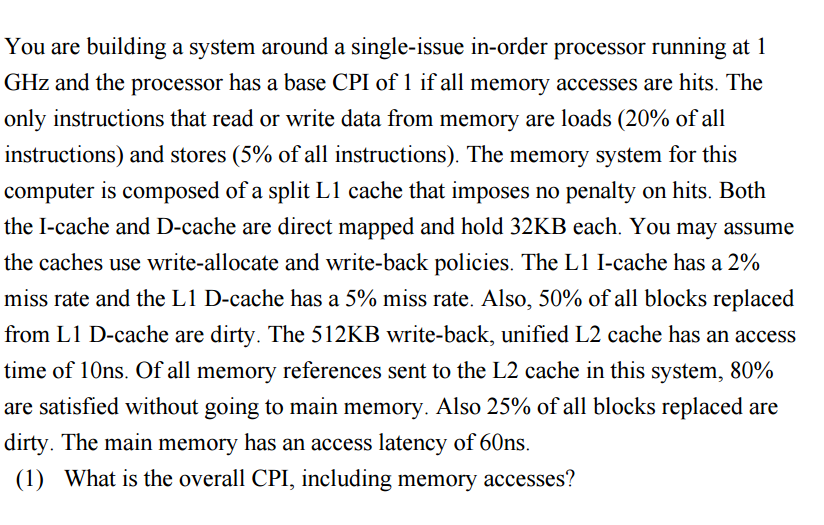

You are building a system around a single-issue in-order processor running at 1 GHz and the processor has a base CPI of1 if all memory accesses are hits. The only instructions that read or write data from memory are loads (20% of all instructions) and stores (5% of all instructions). The memory system for this computer is composed of a split L1 cache that imposes no penalty on hits. Both the I-cache and D-cache are direct mapped and hold 32KB each. You may assume the caches use write-allocate and write-back policies. The L1 I-cache has a 2% miss rate and the L1 D-cache has a 5% miss rate. Also, 50% of all blocks replaced from L1 D-cache are dirty. The 512KB write-back, unified L2 cache has an access time of 10ns. Of all memory references sent to the L2 cache in this system, 80% are satisfied without going to main memory. Also 25% of all blocks replaced are dirty. The main memory has an access latency of 60ns. (1) What is the overall CPI, including memory accesses

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts