Question: You have a virtual memory system with 2-entry TLB, a 2-way set-associate cache and a page table for a process P. Assume cache blocks of

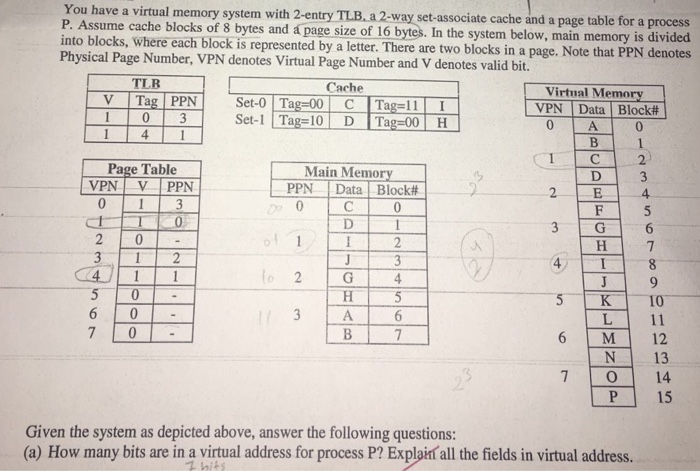

You have a virtual memory system with 2-entry TLB, a 2-way set-associate cache and a page table for a process P. Assume cache blocks of 8 bytes and page size of 16 bytes. In the system below, main memory is divided into blocks, where each block is represented by a letter. There are two blocks in a page. Note that PPN denotes Physical Page Number, VPN denotes Virtual Page Number and V denotes valid bit TLB Cache Virtual Memory VPN | Data | Block# Set-1 [Tag-10 | D I Tag:001 H Page Table VPN | V | PPN Main Memory PPN | Data | Block# 2 -| E H17 4 K110 LI 11 6 M 12 NI 13 ?? 14 P15 6 0 Given the system as depicted above, answer the following questions: (a) How many bits are in a virtual address for process P? Explain all the fields in virtual address

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts