Question: Design a Finite state machine to enable the use of a write buffer. In this exercise, we will explore the control unit for a cache

Design a Finite state machine to enable the use of a write buffer.

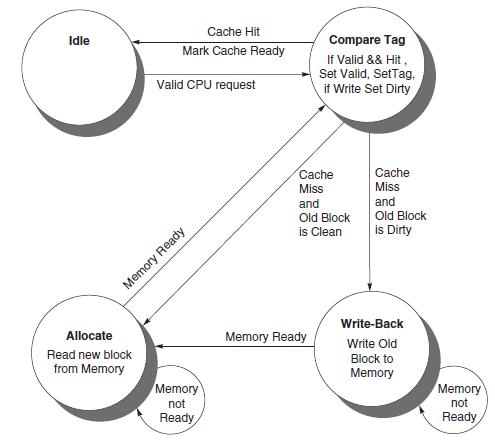

In this exercise, we will explore the control unit for a cache controller for a processor with a write buffer. Use the inite state machine found in Figure 5.34 as a starting point for designing your own inite state machines. Assume that the cache controller is for the simple direct-mapped cache described on page 529, but you will add a write buffer with a capacity of one block. Recall that the purpose of a write buffer is to serve as temporary storage so that the processor doesn't have to wait for two memory accesses on a dirty miss. Rather than writing back the dirty block before reading the new block, it buffers the dirty block and immediately begins reading the new block. The dirty block can then be written to main memory while the processor is working.

Idle Allocate Read new block from Memory Cache Hit Mark Cache Ready Valid CPU request Memory Ready Memory not Ready Compare Tag If Valid && Hit, Set Valid, SetTag, if Write Set Dirty Cache Miss and Old Block is Clean Memory Ready Cache Miss and Old Block is Dirty Write-Back Write Old Block to Memory Memory not Ready

Step by Step Solution

3.42 Rating (149 Votes )

There are 3 Steps involved in it

To design a Finite State Machine FSM for enabling the use of a write buffer in a cache controller we need to outline the various states and transition... View full answer

Get step-by-step solutions from verified subject matter experts