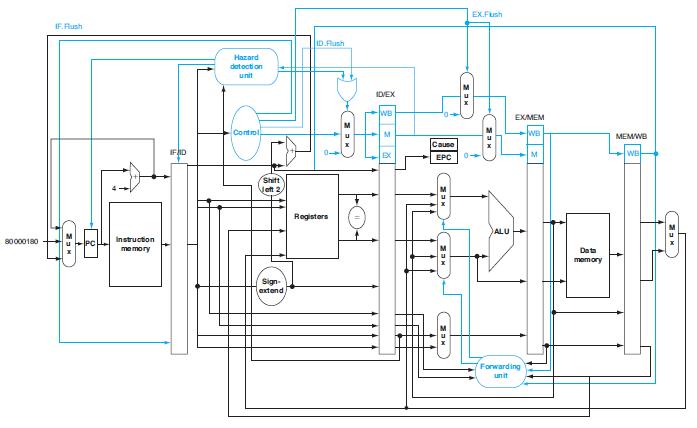

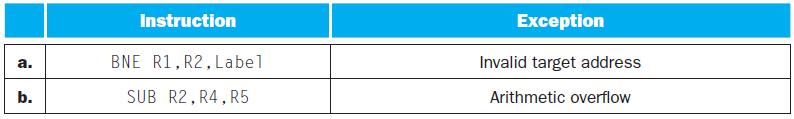

Question: For each stage of the pipeline, determine the values of exception- related control signals from Figure 4.66 as this instruction passes through that pipeline stage.

For each stage of the pipeline, determine the values of exception- related control signals from Figure 4.66 as this instruction passes through that pipeline stage.

This exercise explores how exception handling affects control unit design and processor clock cycle time. The first three problems in this exercise refer to the following MIPS instruction that triggers an exception:

80000180 IF.Rush Instruction mo mory IF ID Hazard detection unit Control Shift Sign- extend ID.Rush Registers U IDVEX WB M EX Cause EPC MON *==++ EX.Flush MUN ALU EX/MEM WB Forwarding unit M Data memory MEMWB WB 4

Step by Step Solution

3.58 Rating (158 Votes )

There are 3 Steps involved in it

Well take the given MIPS instruction and its associated exception and use Figure 466 to determine th... View full answer

Get step-by-step solutions from verified subject matter experts