Question: It is necessary to design a pipeline for a fixed-point multiplier that multiplies two 8-bit binary integers. Each segment consists of a number of AND

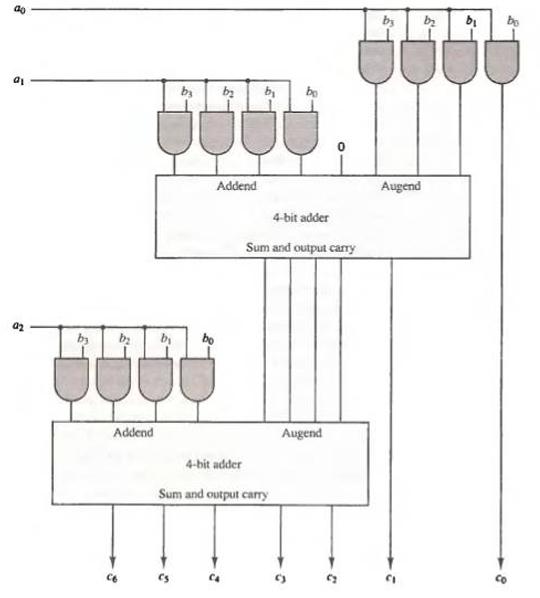

It is necessary to design a pipeline for a fixed-point multiplier that multiplies two 8-bit binary integers. Each segment consists of a number of AND gates and a binary adder similar to an array multiplier as shown in Fig. 10-10.

a. How many AND gates are there in each segment, and what size of adder is needed?

b. How many segments are there in the pipeline?

c. If the propagation delay in each segment is 30 ns, what is the average time that it takes to multiply two fixed-point numbers in the pipeline?

Fig. 10-10

a S by b Addend by by bo b Addend by 4-bit adder Sum and output carry bo 4-bit adder Sum and output carry Augend 0 C Augend b 8- 8

Step by Step Solution

3.42 Rating (155 Votes )

There are 3 Steps involved in it

Lets dissect these questions in order to create the fixedpoint multiplier pipeline A single AND ga... View full answer

Get step-by-step solutions from verified subject matter experts