Question: Compile and simulate the 4-bit adder in Figures 3-47 and 3-48. Apply combinations that check out the rightmost full adder for all eight input combinations;

Compile and simulate the 4-bit adder in Figures 3-47 and 3-48. Apply combinations that check out the rightmost full adder for all eight input combinations; this also serves as a check for the other full adders. Also, apply combinations that check the carry chain connections between all full adders by demonstrating that a 0 and a 1 can be propagated from C0 to C4.

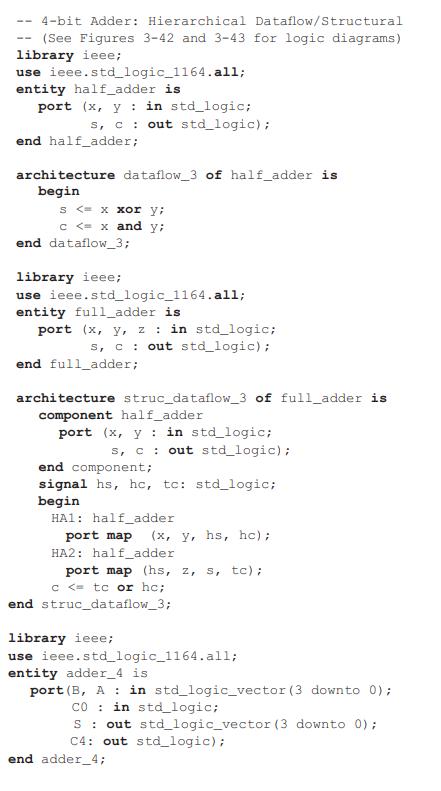

Figure 3-47

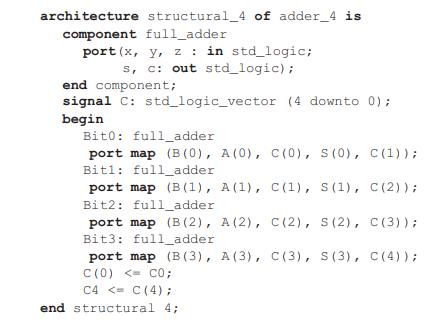

Figures 3-48

--4-bit Adder: Hierarchical Dataflow/Structural (See Figures 3-42 and 3-43 for logic diagrams) library ieee; use ieee.std_logic_1164.all; entity half_adder is. port (x, y: in std_logic; s, c: out std_logic); end half_adder; architecture dataflow_3 of half_adder is begin s

Step by Step Solution

3.41 Rating (148 Votes )

There are 3 Steps involved in it

The VHDL code provided defines a 4bit adder using hierarchical design The design is split into two smaller components a halfadder and a fulladder The ... View full answer

Get step-by-step solutions from verified subject matter experts