Question: 2. Problems in this exercise assume that logic blocks needed to implement a processor's datapath have the following latencies Instruction Memory Add Mux ALU Register

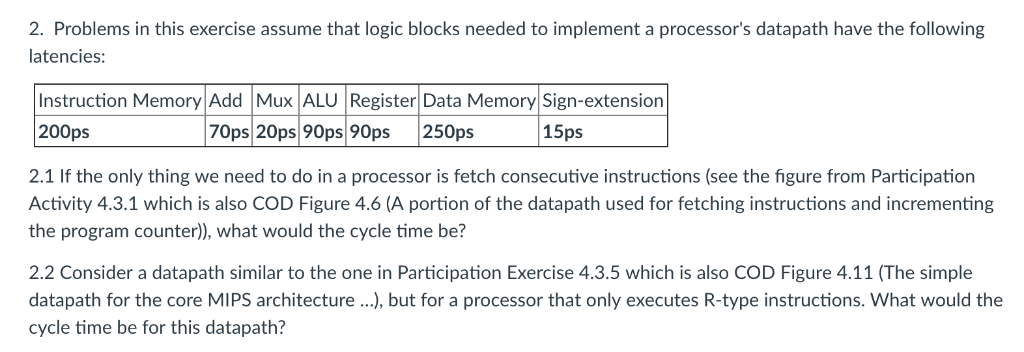

2. Problems in this exercise assume that logic blocks needed to implement a processor's datapath have the following latencies Instruction Memory Add Mux ALU Register Data Memory Sign-extension 200ps 70ps 20ps 90ps 90ps 250ps 15ps 2.1 If the only thing we need to do in a processor is fetch consecutive instructions (see the figure from Participation Activity 4.3.1 which is also COD Figure 4.6 (A portion of the datapath used for fetching instructions and incrementing the program counter)), what would the cycle time be? 2.2 Consider a datapath similar to the one in Participation Exercise 4.3.5 which is also COD Figure 4.11 (The simple datapath for the core MIPS architecture.), but for a processor that only executes R-type instructions. What would the cycle time be for this datapath

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts