Question: Computer Architecture 2. Problem in this exercise assume that logic blocks needed to implement a processor's datapath have the following latencies: -Men Add Mux ALURegs

Computer Architecture

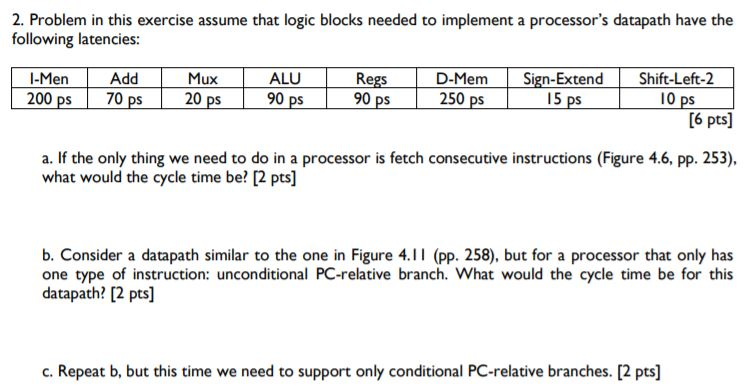

2. Problem in this exercise assume that logic blocks needed to implement a processor's datapath have the following latencies: -Men Add Mux ALURegs D-Mem Sign-Extend Shift-Left-2 200 ps 70 ps 20 ps 90 ps90ps250 ps15 ps0ps (6 pts] a. If the only thing we need to do in a processor is fetch consecutive instructions (Figure 4.6, pp. 253) what would the cycle time be? [2 pts] b. Consider a datapath similar to the one in Figure 4.1 (pp. 258), but for a processor that only has one type of instruction: unconditional PC-relative branch. What would the cycle time be for this datapath? [2 pts] c. Repeat b, but this time we need to support only conditional PC-relative branches. [2 pts]

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts