Question: //32 bit adder //To get all scores, you cannot use arithmetic operators in this module. module adder (input [31:0] x, input [31:0] y, input ci,

//32 bit adder

//To get all scores, you cannot use arithmetic operators in this module.

module adder (input [31:0] x,

input [31:0] y,

input ci,

output reg co,

output reg [31:0] s);

//write your code here

endmodule

![operators in this module. module adder (input [31:0] x, input [31:0] y,](https://dsd5zvtm8ll6.cloudfront.net/si.experts.images/questions/2024/09/66efeb01bf82e_29766efeb015e0ef.jpg)

//32-bit shifter

//To get all scores, you cannot use shift operators in this module.

module shifter (input [31:0] x,

input [4:0] c,

input [1:0] op,

output reg [31:0] y);

//write your code here

endmodule

![input ci, output reg co, output reg [31:0] s); //write your code](https://dsd5zvtm8ll6.cloudfront.net/si.experts.images/questions/2024/09/66efeb0277218_29866efeb02026dd.jpg)

//32-bit ALU

//To get all scores, you cannot use arithmetic operator in this module.

module ALU( input [31:0] x,

input [31:0] b,

input [2:0] op,

output reg [31:0] s);

//write your code here

endmodule

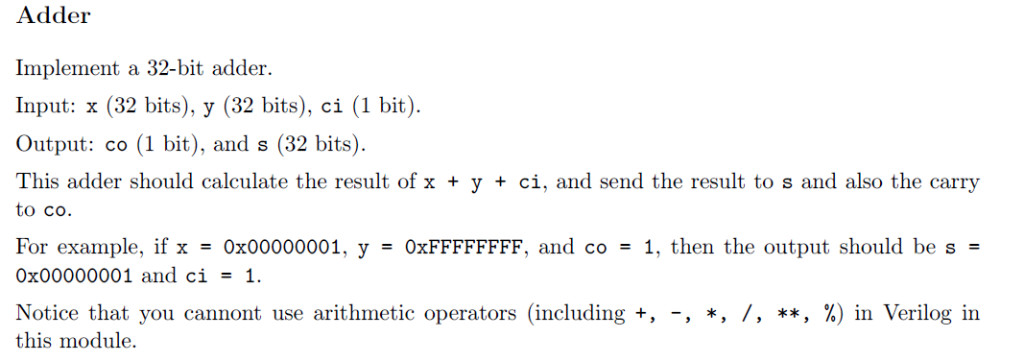

Adder Implement a 32-bit adder Input: x (32 bits), y (32 bits), ci (1 bit). Output: co (1 bit), and s (32 bits). This adder should calculate the result of x y + ci, and send the result to s and also the carry to co. For example, if x = 0:00000001, y = OxFFFFFFFF, and co = 1, then the output should be s = 0x00000001 and ci - 1. Notice that you cannont use arithmetic operators (including +, -, *, /, **, %) in Verilog in this module. ALU Implement a 32-bit ALU. Input: a (32 bits), b (32 bits), and op (3 bits). Output:s(32 bits). The ALU should send the results of operations with a and b to s. The operations are specified by the value of op, as shown in the following table: Assume a0x0000001 and b-0xFFFFFFFF Table 3: Operations of ALU o> opraiion 0 a + b Ox00000000 1a-b0x00000002 2a+ 10x00000002 300x00000000 4a AND b0x00000001 5a OR b OxFFFFFFFF 7NOT a OxFFFFFFF we also show the results of each operations in the above table. Notice that AND, OR, XOR, and NOT operations are bitwise operations. Notice that you cannot use arithmetic operators (including +, -, *, / , **, %) in Verilog in this module, but logical and bitwise operators are allowed

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts