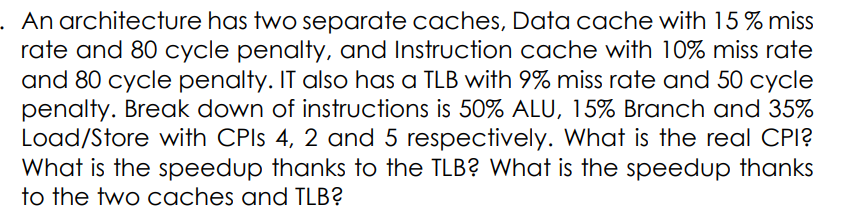

Question: An architecture has two separate caches, Data cache with 1 5 % miss rate and 8 0 cycle penalty, and Instruction cache with 1 0

An architecture has two separate caches, Data cache with miss

rate and cycle penalty, and Instruction cache with miss rate

and cycle penalty. IT also has a TLB with miss rate and cycle

penalty. Break down of instructions is ALU, Branch and

LoadStore with CPIs and respectively. What is the real CPI?

What is the speedup thanks to the TLB What is the speedup thanks

to the two caches and TLBAn architecture has two separate caches, Data cache with miss

rate and cycle penalty, and Instruction cache with miss rate

and cycle penalty. IT also has a TLB with miss rate and cycle

penalty. Break down of instructions is ALU, Branch and

LoadStore with CPIs and respectively. What is the real CPI?

What is the speedup thanks to the TLB What is the speedup thanks

to the two caches and TLB

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock