Question: Consider a multi-cycle floating-point pipelined processor with the four execution units shown below. Depending on the execution unit used, the EXE stage has the following

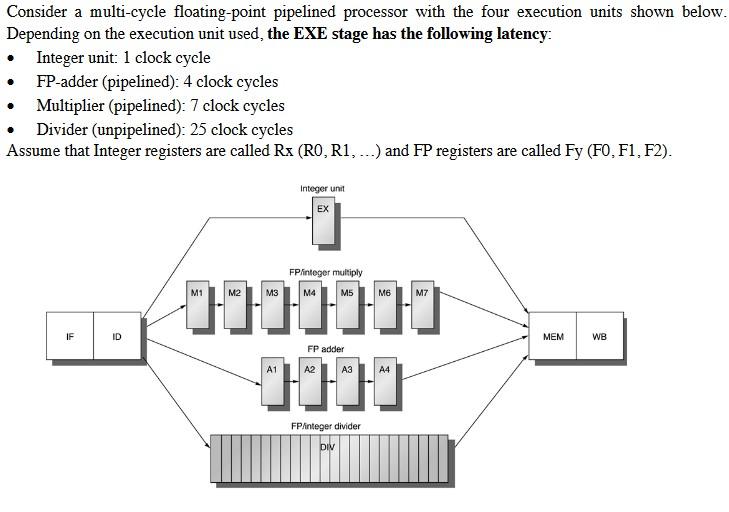

Consider a multi-cycle floating-point pipelined processor with the four execution units shown below. Depending on the execution unit used, the EXE stage has the following latency: Integer unit: 1 clock cycle FP-adder (pipelined): 4 clock cycles Multiplier (pipelined): 7 clock cycles Divider (unpipelined): 25 clock cycles Assume that Integer registers are called Rx (R0, R1, ...) and FP registers are called Fy (F0, F1, F2).

A)Indicate all the hazards present in this code and insert in the code all the STALLS required to resolve them. instructions are numbered just for convenience. MULT1 F1 F2 F3 MULT2 F1 F8 F9 ADD3 F1 F7 F8 SUB4 F2 F1 F5 DIV5 F4 F2 F6

B)Indicate all the hazards present in this code and insert in the code all the STALLS required to resolve them assuming that none of the functional units are pipelined. MULT1 F1 F2 F3 MULT2 F1 F8 F9 ADD3 F1 F7 F8 SUB4 F2 F1 F5 DIV5 F4 F2 F6

Consider a multi-cycle floating-point pipelined processor with the four execution units shown below Depending on the execution unit used, the EXE stage has the following latency: - Integer unit: 1 clock cycle - FP-adder (pipelined): 4 clock cycles - Multiplier (pipelined): 7 clock cycles - Divider (unpipelined): 25 clock cycles Assume that Integer registers are called Rx(R0,R1,) and FP registers are called Fy(F0,F1,F2)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts