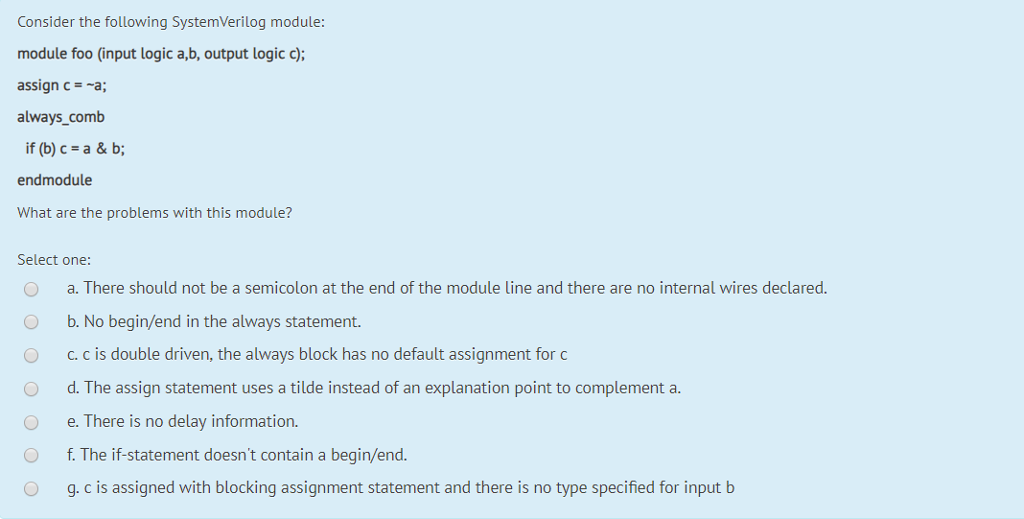

Question: Consider the following SystemVerilog module: module foo (input logic a,b, output logic c); assign ca always_comb if (b) c-a & b; endmodule What are the

Consider the following SystemVerilog module: module foo (input logic a,b, output logic c); assign ca always_comb if (b) c-a & b; endmodule What are the problems with this module? Select one: O a. There should not be a semicolon at the end of the module line and there are no internal wires declared. O b. No begin/end in the always statement. O c.c is double driven, the always block has no default assignment for c O d. The assign statement uses a tilde instead of an explanation point to complement a O e.There is no delay information O f. The if-statement doesn't contain a begin/end. O g. c is assigned with blocking assignment statement and there is no type specified for input b

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts