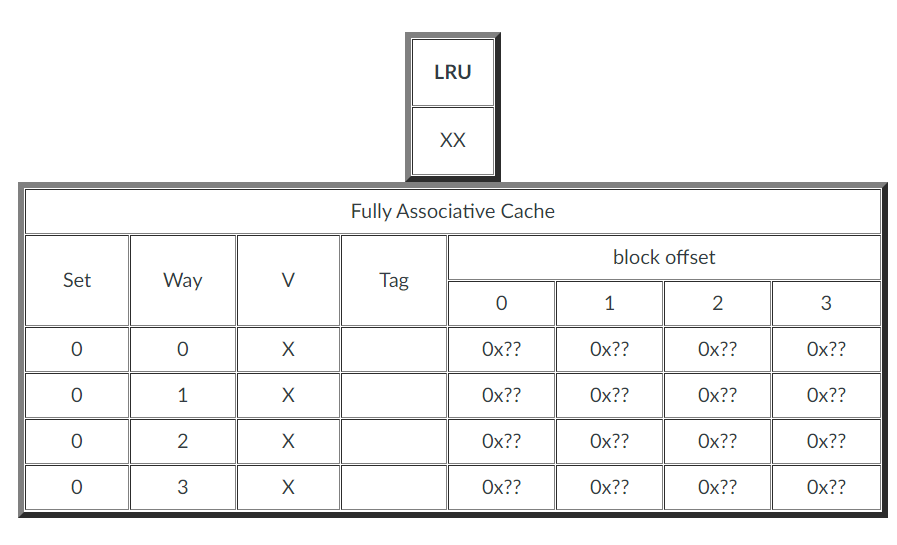

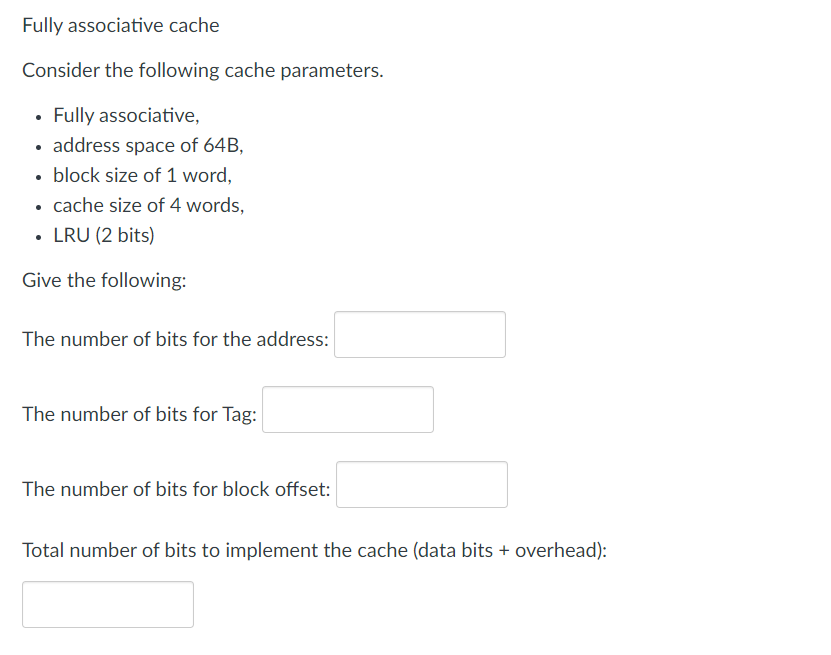

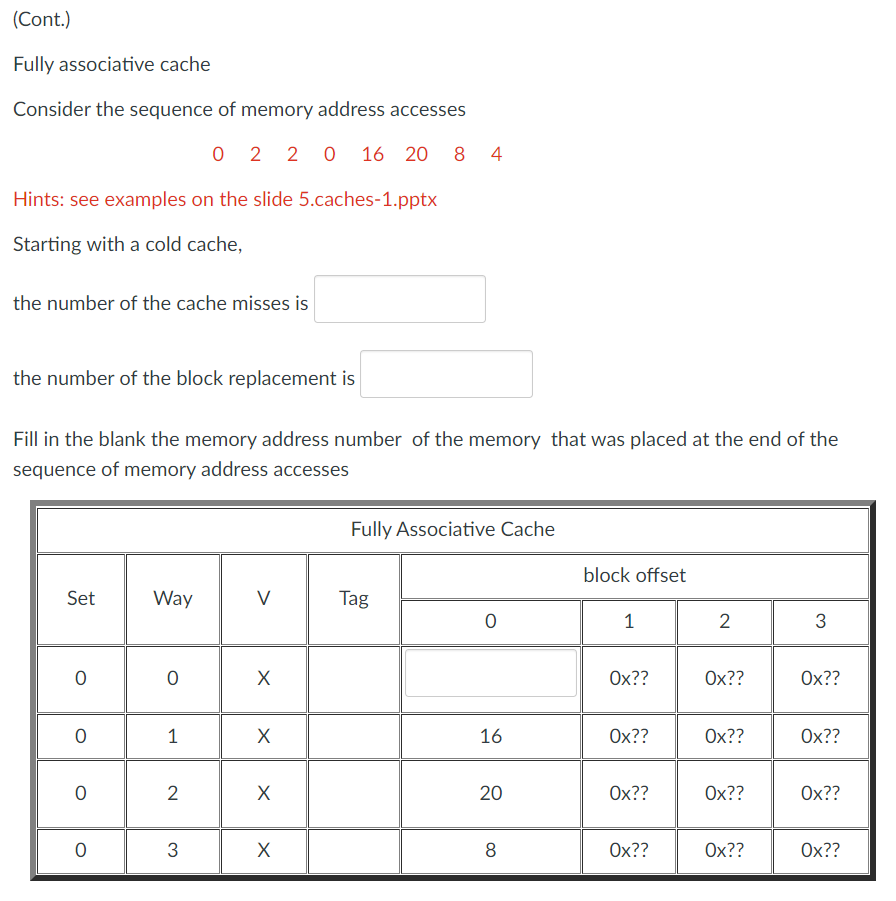

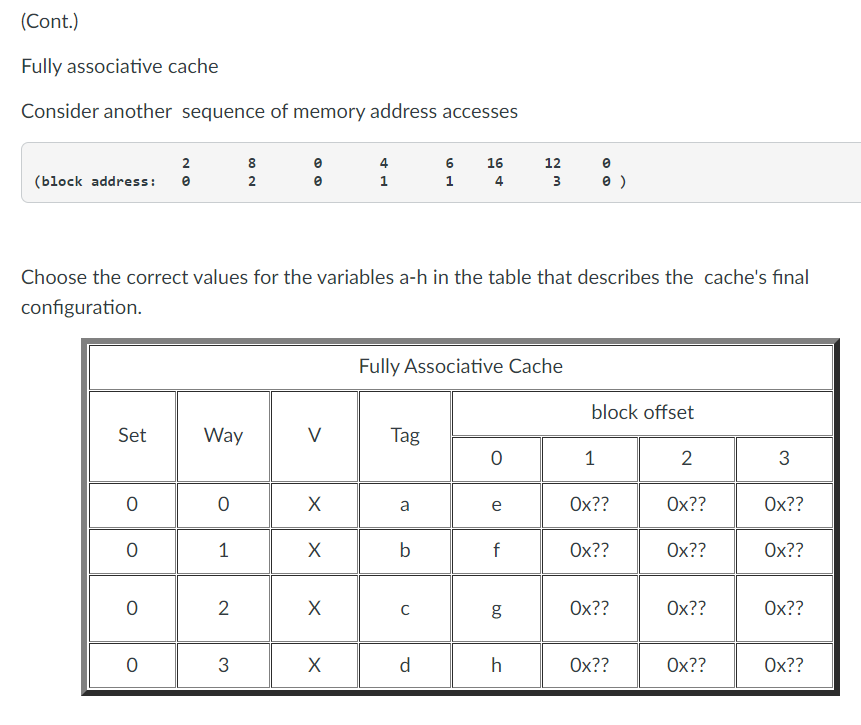

Question: Fully Associative Cache begin{tabular}{|c|c|c|c|c|c|c|c|} hline multirow{2}{*}{ Set } & multirow{2}{*}{ Way } & multirow{2}{*}{V} & multirow{2}{*}{ Tag } & multicolumn{4}{|c|}{ block offset } cline

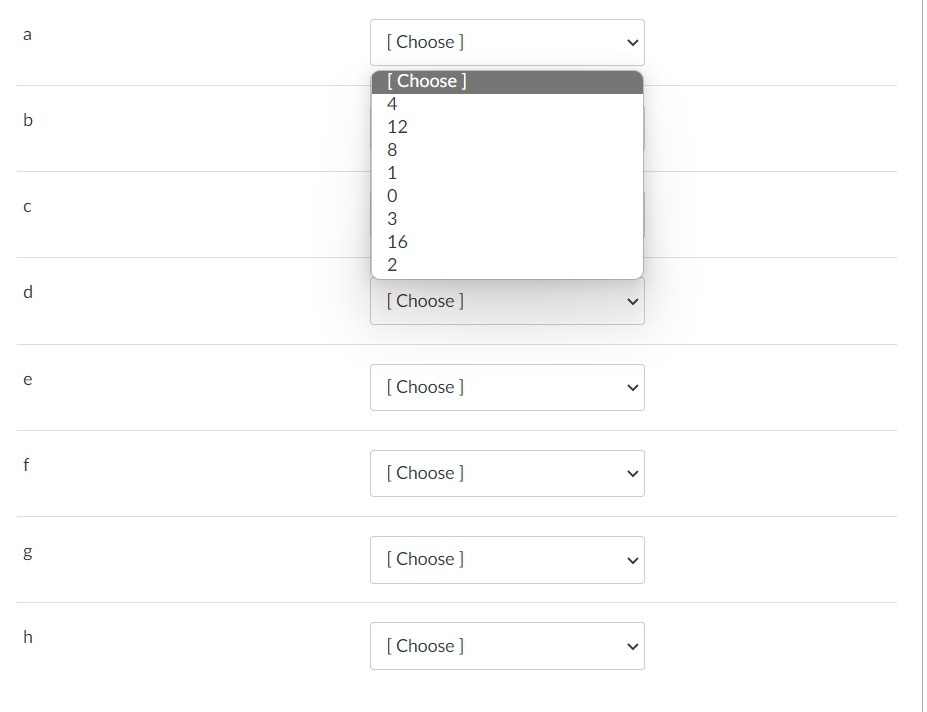

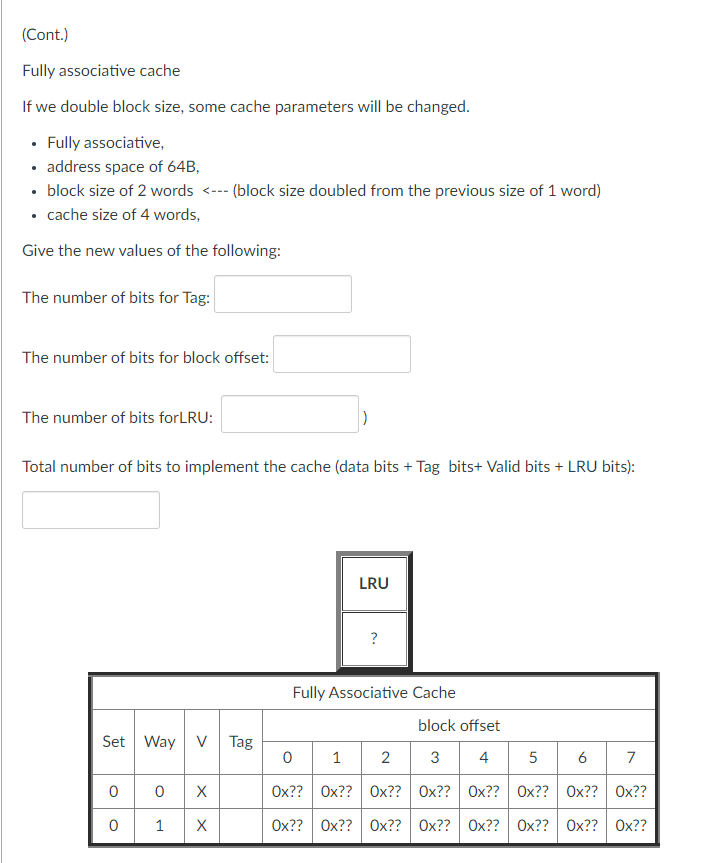

Fully Associative Cache \begin{tabular}{|c|c|c|c|c|c|c|c|} \hline \multirow{2}{*}{ Set } & \multirow{2}{*}{ Way } & \multirow{2}{*}{V} & \multirow{2}{*}{ Tag } & \multicolumn{4}{|c|}{ block offset } \\ \cline { 5 - 8 } & & & & 0 & 1 & 2 & 3 \\ \hline 0 & 0 & X & & 0x?? & 0x?? & 0x?? & 0x?? \\ \hline \hline 0 & 1 & X & & 0x?? & 0x?? & 0x?? & 0x?? \\ \hline 0 & 2 & X & & 0x?? & 0x?? & 0x?? & 0x?? \\ \hline \hline 0 & 3 & X & & 0x?? & 0x?? & 0x?? & 0x?? \\ \hline \hline \end{tabular} Fully associative cache Consider the following cache parameters. - Fully associative, - address space of 64B, - block size of 1 word, - cache size of 4 words, - LRU (2 bits) Give the following: The number of bits for the address: The number of bits for Tag: The number of bits for block offset: Total number of bits to implement the cache (data bits + overhead): (Cont.) Fully associative cache Consider the sequence of memory address accesses Hints: see examples on the slide 5.caches-1.pptx Starting with a cold cache, the number of the cache misses is the number of the block replacement is Fill in the blank the memory address number of the memory that was placed at the end of the sequence of memory address accesses (Cont.) Fully associative cache Consider another sequence of memory address accesses Choose the correct values for the variables a-h in the table that describes the cache's final configuration. \begin{tabular}{l|l|} \hline \multicolumn{1}{l|}{ a } & [Choose ] \\ \hline & {[ Choose ] } \\ \hline b & 4 \\ & 12 \\ & 8 \\ c & 1 \\ & 0 \\ & 3 \\ \hline & 16 \\ & 2 \\ \hline \end{tabular} e [ Choose] f [ Choose] g [ Choose ] h [ Choose] (Cont.) Fully associative cache If we double block size, some cache parameters will be changed. - Fully associative, - address space of 64B, - block size of 2 words Fully Associative Cache \begin{tabular}{|c|c|c|c|c|c|c|c|} \hline \multirow{2}{*}{ Set } & \multirow{2}{*}{ Way } & \multirow{2}{*}{V} & \multirow{2}{*}{ Tag } & \multicolumn{4}{|c|}{ block offset } \\ \cline { 5 - 8 } & & & & 0 & 1 & 2 & 3 \\ \hline 0 & 0 & X & & 0x?? & 0x?? & 0x?? & 0x?? \\ \hline \hline 0 & 1 & X & & 0x?? & 0x?? & 0x?? & 0x?? \\ \hline 0 & 2 & X & & 0x?? & 0x?? & 0x?? & 0x?? \\ \hline \hline 0 & 3 & X & & 0x?? & 0x?? & 0x?? & 0x?? \\ \hline \hline \end{tabular} Fully associative cache Consider the following cache parameters. - Fully associative, - address space of 64B, - block size of 1 word, - cache size of 4 words, - LRU (2 bits) Give the following: The number of bits for the address: The number of bits for Tag: The number of bits for block offset: Total number of bits to implement the cache (data bits + overhead): (Cont.) Fully associative cache Consider the sequence of memory address accesses Hints: see examples on the slide 5.caches-1.pptx Starting with a cold cache, the number of the cache misses is the number of the block replacement is Fill in the blank the memory address number of the memory that was placed at the end of the sequence of memory address accesses (Cont.) Fully associative cache Consider another sequence of memory address accesses Choose the correct values for the variables a-h in the table that describes the cache's final configuration. \begin{tabular}{l|l|} \hline \multicolumn{1}{l|}{ a } & [Choose ] \\ \hline & {[ Choose ] } \\ \hline b & 4 \\ & 12 \\ & 8 \\ c & 1 \\ & 0 \\ & 3 \\ \hline & 16 \\ & 2 \\ \hline \end{tabular} e [ Choose] f [ Choose] g [ Choose ] h [ Choose] (Cont.) Fully associative cache If we double block size, some cache parameters will be changed. - Fully associative, - address space of 64B, - block size of 2 words

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts