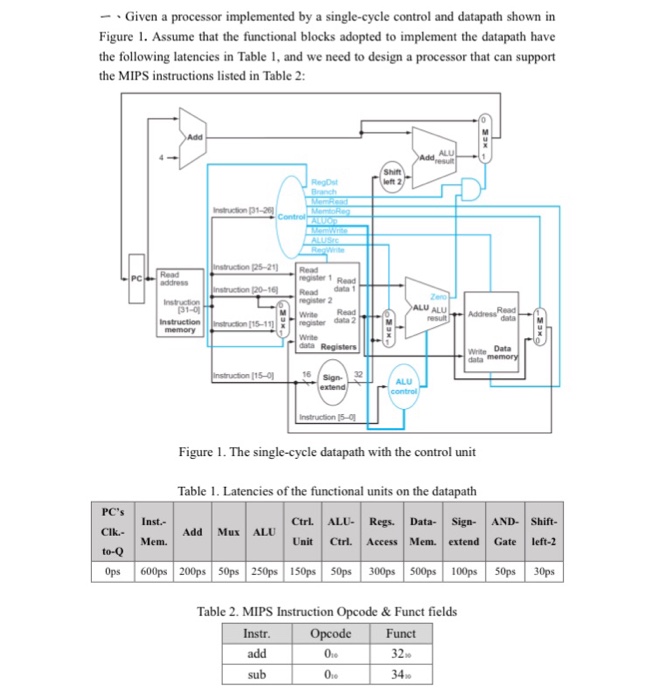

Question: Given a processor implemented by a single-cycle control and datapath shown in Figure1. Assume that the functional blocks adopted to implement the datapath have the

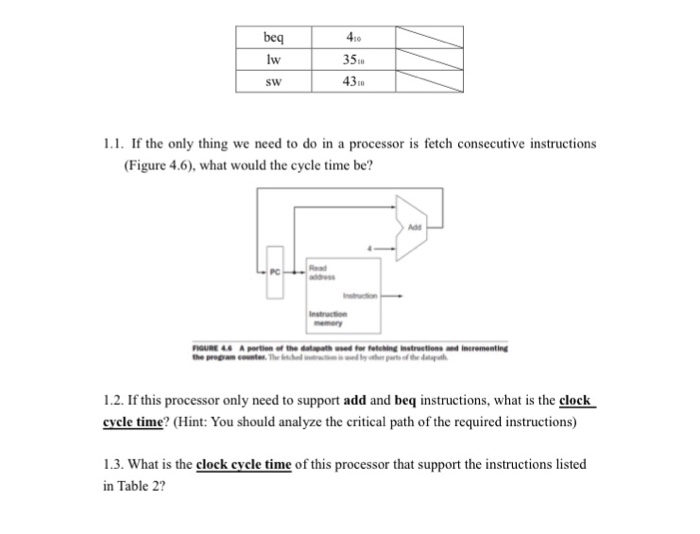

Given a processor implemented by a single-cycle control and datapath shown in Figure1. Assume that the functional blocks adopted to implement the datapath have the following latencies in Table 1, and we need to design a processor that can support the MIPS instructions listed in Table 2: Instruction 31-26 25-21 Read PC -|Read register 2 31-0 WieRead -1ter data2 data Registers Data ALU Figure 1. The single-cycle datapath with the control unit Table 1. Latencies of the functional units on the datapath PC's Inst- Ctri. ALU Regs. Data- Sign-AND- Shift- Unit Ctrl. Access Mem. extend Gate left-2 CIk.- Add Mux ALU Me 0ps 600ps 200ps 50ps 250ps 150ps 50ps 300ps 500ps 100ps 50ps 30ps Table 2. MIPS Instruction Opcode & Funct fields Instr. Opcode Funct 32 su Given a processor implemented by a single-cycle control and datapath shown in Figure1. Assume that the functional blocks adopted to implement the datapath have the following latencies in Table 1, and we need to design a processor that can support the MIPS instructions listed in Table 2: Instruction 31-26 25-21 Read PC -|Read register 2 31-0 WieRead -1ter data2 data Registers Data ALU Figure 1. The single-cycle datapath with the control unit Table 1. Latencies of the functional units on the datapath PC's Inst- Ctri. ALU Regs. Data- Sign-AND- Shift- Unit Ctrl. Access Mem. extend Gate left-2 CIk.- Add Mux ALU Me 0ps 600ps 200ps 50ps 250ps 150ps 50ps 300ps 500ps 100ps 50ps 30ps Table 2. MIPS Instruction Opcode & Funct fields Instr. Opcode Funct 32 su

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts