Question: http://www.ecs.umass.edu/ece/koren/architecture/SVCache/default.htm Use this site CHAPTER 4: CACHE TIME ANALYSIS 1) Consider a 4-way set associative cache of size 4KB and block size of 64bytes. Consider

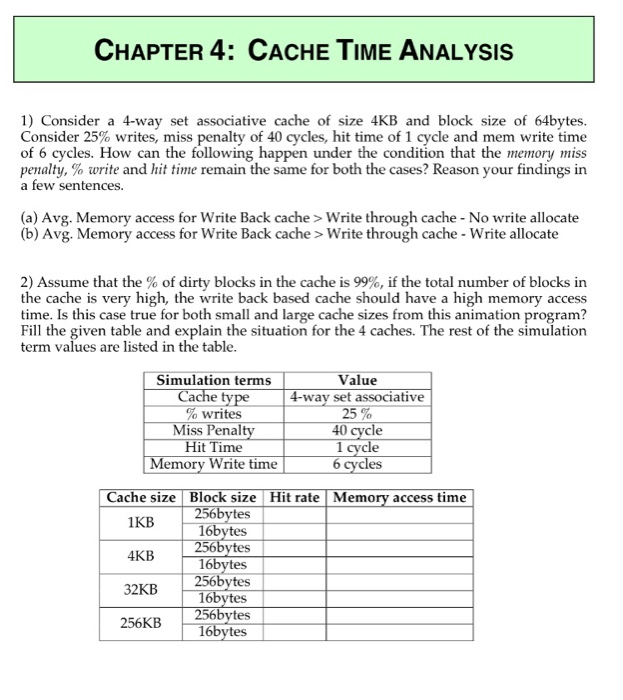

CHAPTER 4: CACHE TIME ANALYSIS 1) Consider a 4-way set associative cache of size 4KB and block size of 64bytes. Consider 25% writes, miss penalty of 40 cycles, hit time of 1 cycle and mem write time of 6 cycles. How can the following happen under the condition that the memory miss penalty, % write and hit time remain the same for both the cases? Reason your findings in a few sentences. (a) Avg. Memory access for Write Back cache> Write through cache No write allocate (b) Avg. Memory access for Write Back cache> Write through cache- Write allocate 2) Assume that the % of dirty blocks in the cache is 99%, if the total number of blocks in the cache is very high, the write back based cache should have a high memory access time. Is this case true for both small and large cache sizes from this animation program? Fill the given table and explain the situation for the 4 caches. The rest of the simulation term values are listed in the table. Simulation terms Value Cache type 4-y set associati writes 25 ss Pena 40 it Time emor rite time es Cache size Block size Hit rate Memory access time 1KB 4KB 32KB ytes es bytes 256KB 256 es CHAPTER 4: CACHE TIME ANALYSIS 1) Consider a 4-way set associative cache of size 4KB and block size of 64bytes. Consider 25% writes, miss penalty of 40 cycles, hit time of 1 cycle and mem write time of 6 cycles. How can the following happen under the condition that the memory miss penalty, % write and hit time remain the same for both the cases? Reason your findings in a few sentences. (a) Avg. Memory access for Write Back cache> Write through cache No write allocate (b) Avg. Memory access for Write Back cache> Write through cache- Write allocate 2) Assume that the % of dirty blocks in the cache is 99%, if the total number of blocks in the cache is very high, the write back based cache should have a high memory access time. Is this case true for both small and large cache sizes from this animation program? Fill the given table and explain the situation for the 4 caches. The rest of the simulation term values are listed in the table. Simulation terms Value Cache type 4-y set associati writes 25 ss Pena 40 it Time emor rite time es Cache size Block size Hit rate Memory access time 1KB 4KB 32KB ytes es bytes 256KB 256 es

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts