Question: I have the Project procedural as this: module Project 2 _ procedural ( input A , input B , input C , output F )

I have the Project procedural as this:

module Projectprocedural

input A

input B

input C

output F

;

reg F;

always @ A B C

if A & B & C C

begin

F b;

end

else if A & B & C

begin

F b;

end

else if A & B & C

begin

F b;

end

else if A & B & C

begin

F b;

end

else if A & B & C

begin

F b;

end

else if A & B & C

begin

F b;

end

else if A & B & C

begin

F b;

end

endmodule

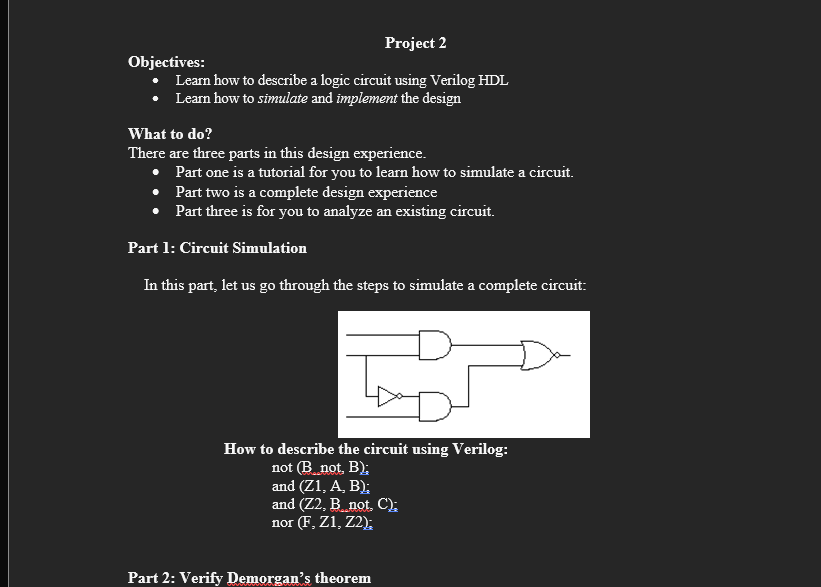

I have the structural is this:

module projectStructural

input A

input B

input C

output F

;

not Bnot, B;

or Z A B;

or Z Bnot, C;

nand F Z Z;

endmodule

I have the continous as this:

module projectcontinous

input A

input B

input C

output F

;

assign F ~AB&~BC;

endmodule

And I have the constraint as this:

setproperty dict PACKAGEPIN J IOSTANDARD LVCMOSgetports A ; #IOLNTRS Schsw

setproperty dict PACKAGEPIN L IOSTANDARD LVCMOSgetports B ; #IOLNTDQSEMCCLK Schsw

setproperty dict PACKAGEPIN M IOSTANDARD LVCMOSgetports C ; #IOLNTDVREF Schsw

setproperty dict PACKAGEPIN H IOSTANDARD LVCMOSgetports F ; #IOLPTA Schled

What is wrong with the code and how do I get it to work? I tried to the bitstream to work with this and it's simply not working.

Common 'setproperty' expects at least one object. C:UsersKFCDesktopLolprojectprojectsrcsconstrsnewProjConstraint.xdc:

Vivado No ports matched FC:UsersKFCDesktopLolprojectprojectsrcsconstrsnewProjConstraint.xdc:

Synth done synthesizing module 'ProjectPartStructural' #C:UsersKFCDesktopLolprojectprojectsrcssourcesnewProjectPartStructural.v:

Synth synthesizing module 'ProjectPartStructural' C:UsersKFCDesktopLolprojectprojectsrcssourcesnewProjectPartStructural.v:

Synth undeclared symbol Anot', assumed default net type 'wire' C:UsersKFCDesktopLolprojectprojectsrcssourcesnewProjectPartStructural.v:

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock