Question: InstructionInstruction! IFetch 2! Memory1Memory 2 Decode /Register Read Execute Fetch 1 I Back BranchI Wnite Write Addr Data Data Memory Read Register Addr Filed [20:16]

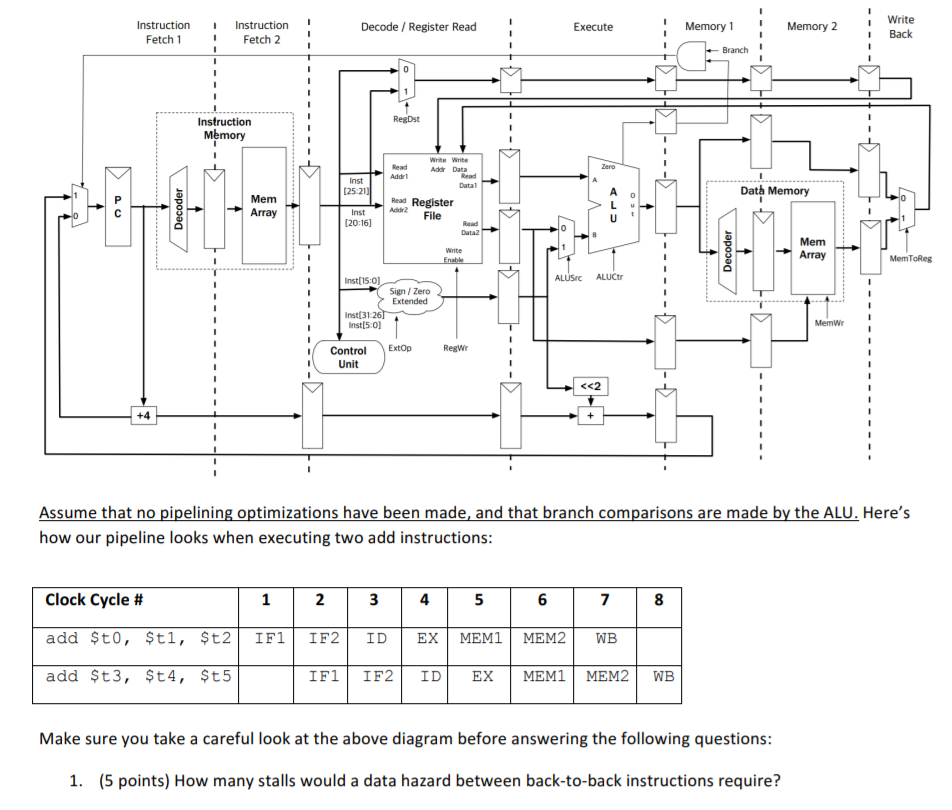

InstructionInstruction! IFetch 2! Memory1Memory 2 Decode /Register Read Execute Fetch 1 I Back BranchI Wnite Write Addr Data Data Memory Read Register Addr Filed [20:16] MemToReg Inst[15:0] ALUSrc ALUCtr Sign / Zero Inst[31 nst[5 0 Memwr Control Extop IUnit Assume that no pipelining optimizations have been made, and that branch comparisons are made by the ALU. Here's how our pipeline looks when executing two add instructions Clock Cycle # add $t0, $t1, $t2| 1F1| 1F2 | ID | EX| MEM?| MEM2| WB add $t3, $t4, $t5 4 5 6 Make sure you take a careful look at the above diagram before answering the following questions: 1. (5 points) How many stalls would a data hazard between back-to-back instructions require

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts