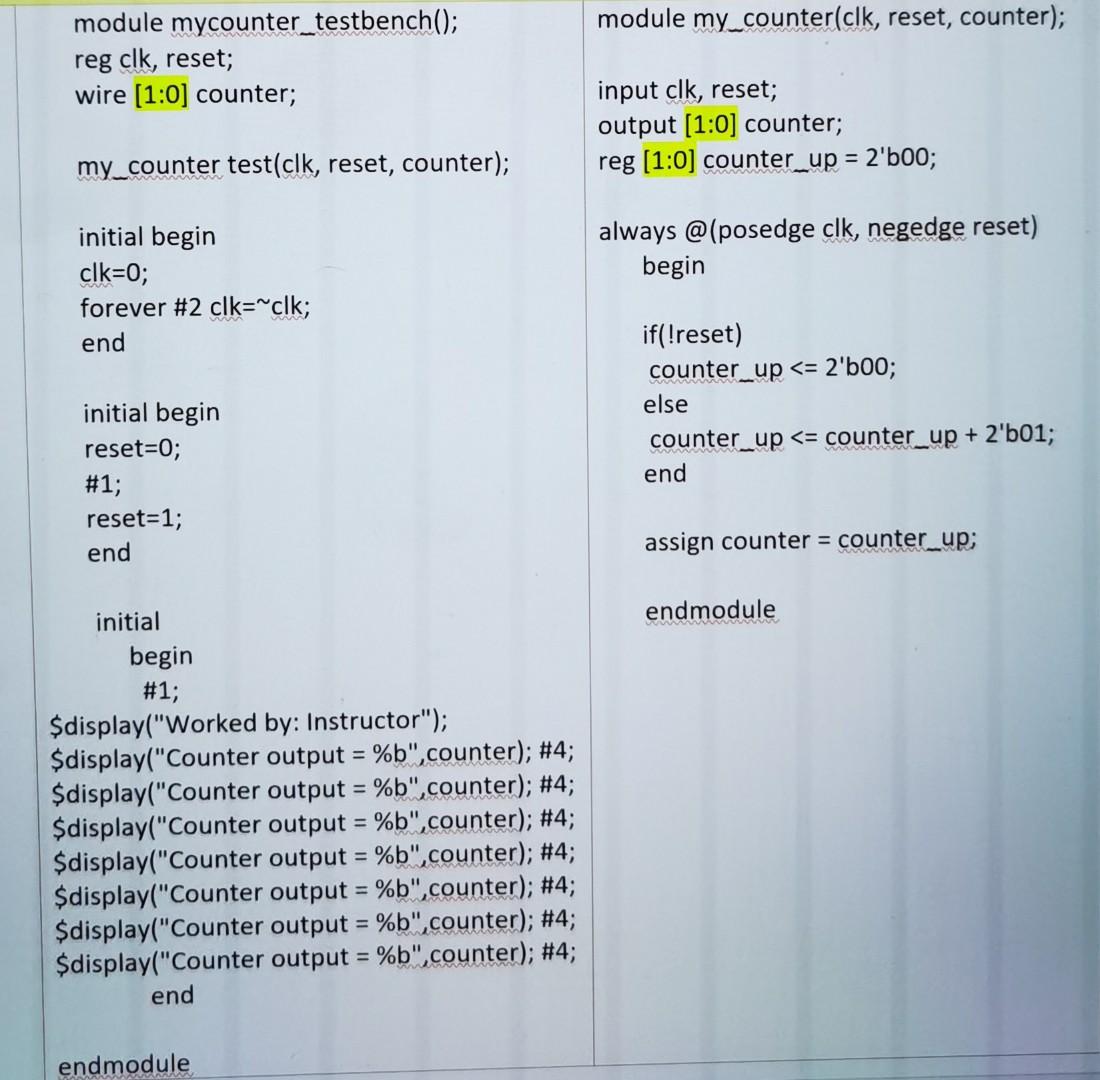

Question: module my counter(clk, reset, counter); module mycounter_testbench(); reg clk, reset; wire (1:0) counter; input clk, reset; output (1:0) counter; reg (1:0) counter_up = 2'b00; my

module my counter(clk, reset, counter); module mycounter_testbench(); reg clk, reset; wire (1:0) counter; input clk, reset; output (1:0) counter; reg (1:0) counter_up = 2'b00; my counter test(clk, reset, counter); always @(posedge clk, negedge reset) begin initial begin clk=0; forever #2 clk=clk; end initial begin reset=0; if(!reset) counter_up

Step by Step Solution

There are 3 Steps involved in it

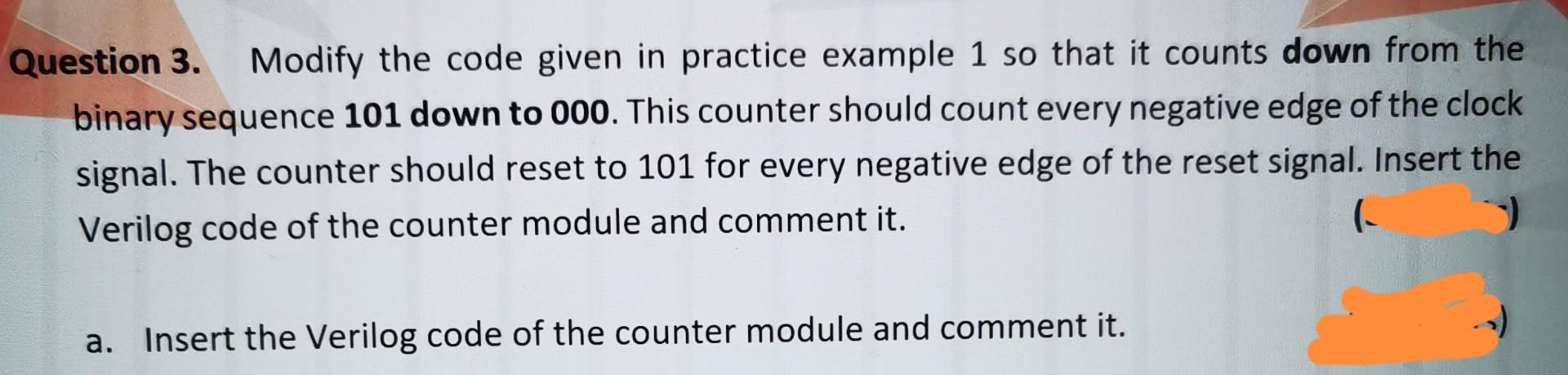

Get step-by-step solutions from verified subject matter experts